## A RISC-V Based Virtual Prototype with an Integrated Hardware-in-the-Loop Radar

Denis Zeinel, Peer Adelt, Bastian Koppelmann, Wolfgang Mueller, Christoph Scheytt Heinz Nixdorf Institut/Universität Paderborn Paderborn, Germany

Our demonstration shows a small radar sensor in interactive communication with a RISC-V processor board and a RISC-V Virtual Prototype (VP) where the VP and the processor concurrently execute exactly the same target compiled software without a visible difference in reaction time. This demonstrates that widely available open source based virtual prototyping environments provide an adequate, stable, and efficient framework for the analysis of such embedded applications.

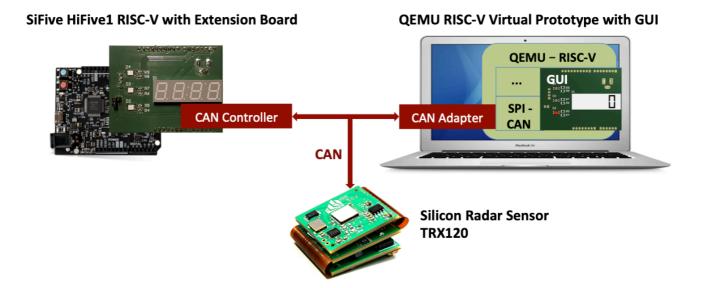

## Joint Hardware and Virtual Prototype Setup

The demonstration integrates our in-house developed 120GHz radar sensor via CAN bus with the SiFive RISC-V HiFive1 development board and our QEMU based VP. For the HiFive1 integration, we developed an Ardunio compliant extension board with an SPI-CAN adapter and a display. For the VP integration, we implemented the same components as QEMU QOM hardware models. Though the VP is executed in a linux based VirtualBox virtual machine on top of an additional host operating system, the impact of both is not visible in this setup.