## Multi-Dataflow Composer Tool

Dataflow-to-hardware composition and optimization of reconfigurable accelerators

Francesca Palumbo\*, Carlo Sau<sup>‡</sup>, Tiziana Fanni<sup>‡</sup>, Claudio Rubattu<sup>\*†</sup>, and Luigi Raffo<sup>‡</sup>

\*University of Sassari, 07100 Sassari, Italy (email: fpalumbo@uniss.it, crubattu@uniss.it)

<sup>‡</sup>University of Cagliari, 09123 Cagliari, Italy (email: name.surname@diee.unica.it)

<sup>†</sup>Univ Rennes, INSA Rennes, IETR UMR CNRS 6164, 35700 Rennes, France

Abstract—UNICA-Eolab and UNISS-IDEA booth is demonstrating the capabilities of the Multi-Dataflow Component tool: a model-based toolset for design and development of virtual coarsegrain reconfigurable circuits providing substrate composition, optimization and integration in real environments.

*Index Terms*—coarse-grained reconfiguration, virtual reconfiguration, FPGA, ASIC, composition, power-management, DSE, datapath-merging, dataflow

## I. INTRODUCTION

Embedded computing systems are pervasive and used in many different application fields such as smart cities, transportation, etc. Complex and distributed infrastructures are required to meet functional and non-functional requirements, associated with dynamic and variable behaviours, real-time constraints and efficient system consumption, which tend to collide. To enable system efficiency, along with optimal energy management, heterogeneous substrates can be used, where reconfigurability can master the required flexibility degree. In particular, Coarse-Grained (CG) virtually reconfigurable accelerators enable supporting several different functionalities, while providing optimal performance. Implementable both in ASIC and on FPGAs, with their modularity they allow deep customization and optimization of the involved elements. Nevertheless, they are affected by Design, Debug and Mapping issues. Custom hardware designs imply to describe the microarchitecture at the RTL level; application details have to be known, requiring effort in coding and debugging. Moreover, dimensioning the underlying structure and mapping multimodal/multi-functional applications over it are challenging.

## II. THE MULTI-DATAFLOW COMPOSER

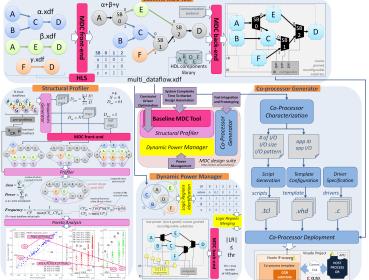

The Multi-Dataflow Composer (MDC) tool is a software framework for automatic generation and management of CG reconfigurable systems, based on the dataflow model of computation. Its components, depicted in Figure 1, are:

- Baseline Core performing dataflow-to-hardware composition, by means of datapath merging techniques [1]. Kernels are provided as dataflow networks, and target agnostic RTL description is derived. [FPGA/ASIC]

- Structural Profiler exploring the design space of the implementable multi-functional systems. Optimal substrate is chosen on the basis of the given frequency and area constraints [1]. [ASIC]

- 3) Dynamic Power Manager performing model-level logic partitioning of the substrate to determine optimal

power/clock domains, and apply saving strategies [2], [3]. [FPGA/ASIC]

Co-Processor Generator - customizing a Xilinx-compliant multi-functional IP with its APIs. [FPGA]

MDC has been already successfully adopted in different applications fields, like multi-media coding [1] and neural signal decoding [4]. Videos and tutorials can be found at [5].

Fig. 1. MDC tool and its extension.

Acknowledgment: Authors thank CERBERO (ID: 732105) and FitOptiVis (ID: 783162) projects, where MDC is developed/extended. UNISS also thanks the Region of Sardinia for funding PROSSIMO project (POR FESR 2014/20-ASSE I), which partly enables MDC technology transfer.

## REFERENCES

- F. Palumbo *et al.*, "Power-awarness in coarse-grained reconfigurable multi-functional architectures: a dataflow based strategy," *Journal of Signal Processing Systems*, 2016. doi:10.1007/s11265-016-1106-9.

- [2] T. Fanni *et al.*, "Automated Power Gating Methodology for Dataflowbased Reconfigurable Systems," in *Conf. on Computing Frontiers*, 2015. doi:10.1145/2742854.27472855.

- [3] T. Fanni *et al.*, "Power and Clock Gating Modelling in Coarse Grained Reconfigurable Systems," in *Conf. on Computing Frontiers*, 2016. doi:10.1145/2903150.2911713.

- [4] N. Carta et al., "A Coarse-Grained Reconfigurable Wavelet Denoiser Exploiting the Multi-Dataflow Composer Tool," in Conf. on Design and Architectures for Signal and Image Processing, 2013.

- [5] https://www.youtube.com/c/ideaLabUniss.