Institute of Electromechanical and Electronic Design

## **MICROPLAN:**

# **Micro-System Design and Production-Planning Tool**

Tilman Horst, Robert Fischbach and Jens Lienig

Why Our Tool is Developed

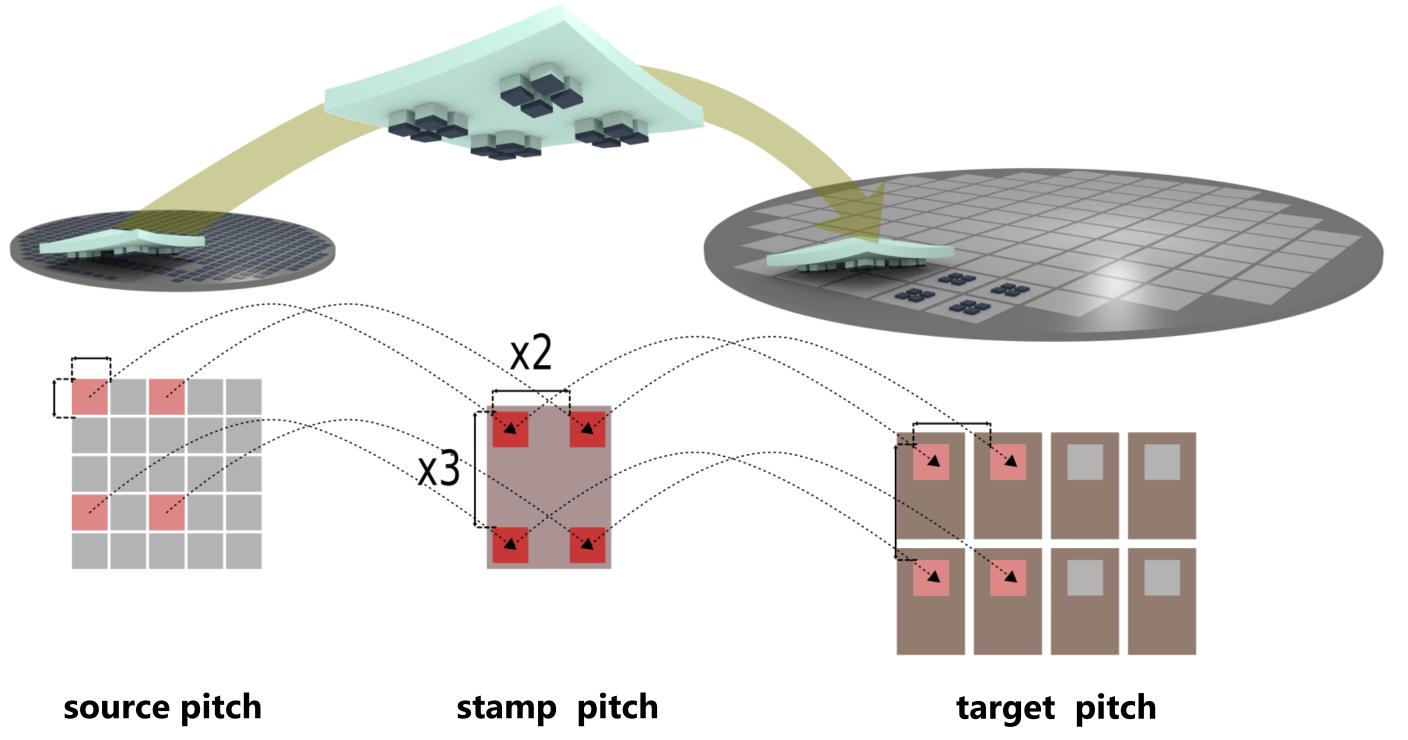

Wafer and Stamp Compatibility

Our tool is developed within the MICROPRINCE project in close cooperation with X-Fab. The goal of the project is the industrialization of the micro-transfer printing process. Micro-transfer printing uses a micro-structured elastomer stamp to transfer dies between wafers. The main features are:

- Massive parallelization of die transfer to reduce processing time and cost

- Transfer between wafers of different sizes (e.g. 6-inch to 8-inch)

- Transfer of dies of different sizes

However, to benefit from these opportunities the wafers hosting the dies need to be compatible with each other as well as with the elastomer stamp executing the transfer. This requires an intelligent design of the components, wafers and stamp and makes co-design essential. Our tool is meant to be used by designers to define the dimensions of system components prior to their work on the IClayouts.

For further information on MICROPRINCE: <u>https://microprince.eu/</u>

#### How to Get

To run the tool no installation is required. Just open an internet browser and type the URL or scan the QR Code with your smartphone/ tablet. When asked provide the username and password.

URL: <u>https://efteweb.et.tu-dresden.de/DATE19/</u>

The target pitch has to be an integer multiple (1, 2, 3, ...) of the source pitch. The stamp pitch has to be an integer multiple of the source and the target pitch at the same time. In the example above the target pitch is two times the source pitch in horizontal und three times the source pitch in vertical direction. Stamp pitch and target pitch are equal.

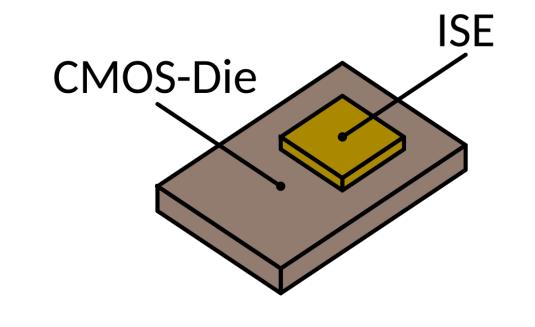

### Heterogeneous Design Example

In this small design example we assume we want to design and manufacture 100,000 integrated infrared sensors. The main components of the system are a CMOS-circuit and the actual infrared sensing element (ISE). The CMOS die is processed on a 8-inch (200 mm) Si wafer. The ISE, however, originates from a 6-inch (150 mm) GaAs wafer. Use the tool to find a layout for such a system with minimum manufacturing costs!

#### How to Use

Use the simple layout editor on the bottom right to define the system layout.

| left click:                    | add a source die to the layout |

|--------------------------------|--------------------------------|

| ctrl + left click:             | remove a source die            |

| <pre>shift + left click:</pre> | move the source die            |

| scroll wheel:                  | zoom in/ out                   |

In case of multiple dies, the positions of the dies cannot be chosen freely (see "Wafer and Stamp Compatibility"), due to restrictions of the transfer printing process. The tool makes sure you are placing your dies in the right place.

Further specify your design by changing the parameters for e.g. wafer size, die size or the pitch between the dies on the wafers.

The table below shows the given parameters. The remaining parameters can be chosen freely! Show us your solution! The solution with the lowest package-unit costs wins a price!

| <b>Geometrical Parameters</b> |                                     |

|-------------------------------|-------------------------------------|

| source-wafer diameter         | 150 mm (6-inch)                     |

| target-wafer diameter         | 200 mm (8-inch)                     |

| source-die area               | 0.1225 mm² (e.g. 350 μm x 350 μm)   |

| source-wafer scribe line      | > 30 μm                             |

| target-die area               | 1.1664 mm² (e.g. 1080 μm x 1080 μm) |

| target-wafer scribe line      | 80 µm                               |

| <b>Cost Parameters</b>        |                                     |

| quantity                      | 100,000                             |

| source-wafer costs            | 4000€                               |

| target-wafer costs            | 6000€                               |

| machine-hour rate             | 2000€                               |

|                               |                                     |

Click on the button **optimize stamp size** to find the cost-optimal stamp size for your design.

The Microprince project has received funding from the European Union's H2020 Programme (ECSEL) under grant agreement number 737465. The Subproject of TU Dresden in Microprince project has received funding from the Bundesministerium für Bildung und Forschung of Germany and from the Staatsministerium für Wirtschaft, Arbeit und Verkehr of the Freistaat Sachsen under grant agreement number 16ESE0231S.

Postal Address Technische Universitaet Dresden Institut fuer Feinwerktechnik und Elektronik-Design 01062 Dresden, Germany *Visitors* Helmholtzstraße 18 01069 Dresden, Germany Barkhausenbau BAR II/20 D *Website* www.ifte.de