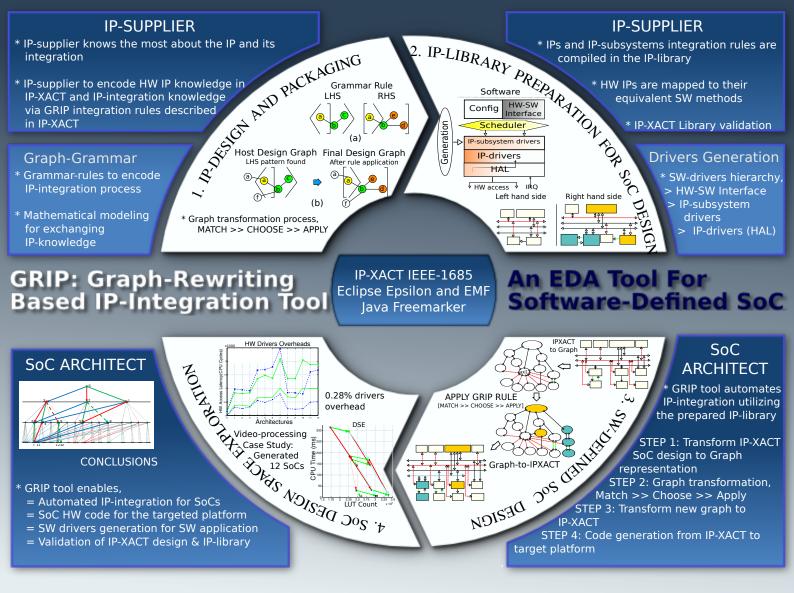

Abstract-The GRIP tool - Graph-Rewriting-Based IP-Integration - provides system engineers with a comprehensive platform that takes care of their IP-integration concerns for IP-centric SoC designs, also referred to as SW-defined SoCs. The tool uses the standardized meta-data IP-XACT format for electronic system descriptions and encodes the design IP-integration knowledge as a set of integration rules based on graph rewriting and graph grammar theory. The tool automates and encodes the step-by-step integration of IPs to build a desired system architecture. Multiple sequential IP-integration steps can be compiled to iteratively generate new system architectures. For design space exploration (DSE) constraints can be given to generate a desired subset of candidate SoC architectures. Code generation is used to generate the design files for each architecture. This is demonstrated for integrating HW acceleration into an OpenCV computer vision application running on a Xilinx Zynq chipset based Zedboard. GRIP additionally generates the HW-drivers for both bare-metal and Linux-based systems [1] [2] [3].

1. IP-DESIGN AND PACKAGING - One major challenge in the IP-centric design is IP-supplier's lacking knowledge of targeted SoCs and SoC architect's lacking knowledge of the supplied hardware IPs. Using the principles of graph-grammar and graph-rewriting, GRIP provides a way to encode IP-integration knowledge by grammar-rules, namely GRIP integration rules. An IP supplier can write these rules in IP-XACT, and GRIP internally transform those to graphs [1]. GRIP generates SW drivers using from the rules for IP-packaging[3].

2. IP-LIBRARY PREPARATION FOR SoCs - An SoC architect assimilate the supplied IP-packages to prepare an IP-library. Using GRIP, an SoC architect can customize the library IPs, rules, and SW drivers. He/She can also generate the drivers

for custom IP-subsystems, using IPs from various vendors. GRIP supports validation of IP-XACT IP-library and integration rules.

3. SW-DEFINED SoC DESIGN - In the GRIP platform, using the IP-library, an SoC architect can cumulatively apply the rules to design desired SoC. He/She can utilize generated drivers to HW accelerate SW methods of the SW application. An IP-integration in GRIP takes four steps, as explained in the figure above. GRIP validates each generated SoC.

4. SoC DESIGN SPACE EXPLORATION (DSE) - While performing DSE for a SW application, an architect can opt for incrementally adding new HW IPs, in the step-by-step exploration mode. Otherwise, an architect can constrain the design space by architecture constraints, and GRIP follows these constraints to generate candidate SoC architectures.

A case study was executed to perform DSE for a videoprocessing application on the Xilinx Zynq FPGA (ZedBoard). The IP-library had 3 HW accelerators and 8 GRIP rules. With DSE constraints, GRIP generated 12 candidate architectures [1].

## REFERENCES

- M. Jassi, D. Mueller-Gritschneder, and U. Schlichtmann. GRIP: Grammar-Based IP Integration and Packaging for Acceleration-Rich SoC Designs. *Design Automation Conference (DAC)*, June 2015.

- [2] M. Jassi, B. Bordes, D. Mueller-Gritschneder, and U. Schlichtmann. Automation of FPGA Performance Monitoring and Debugging Using IP-XACT and Graph-Grammars. *Internation Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD)*, Sept 2015.

- [3] M. Jassi, U. Sharif, D. Mueller-Gritschneder, and U. Schlichtmann. Hardware-Accelerated Software Libraries Drivers Generation for IP-Centric SoC Designs. *Great Lake Symp. VLSI (GLSVLSI)*, 2016 (SUBMITTED).