# Sensitivity-based Modeling and Methodology For Full-Chip Substrate Noise Analysis

Rajeev Murgai, Subodh M. Reddy, Takashi Miyoshi, Takeshi Horie Fujitsu Laboratories of America, Inc. Sunnyvale, CA, USA {murgai,subodh,miyoshi,horie}@fla.fujitsu.com

Mehdi Baradaran Tahoori\*

Northeastern University

Boston, MA, USA.

mtahoori@ece.neu.edu

### Abstract

Substrate noise (SN) is an important problem in mixed-signal designs. With increasing design complexity, it is not possible to simulate for SN with a detailed SPICE model that uses an accurate model for each transistor. In this paper, we propose a sensitivity analysis- and static timing analysis-based methodology to derive a reduced model that computes the worst case substrate noise in the design. The reduced model contains only passive components, which are very few, and is very quick to simulate. The main feature of our methodology is that, unlike previous approaches, it is independent of input patterns and does not need to simulate for millions of clock cycles. This lets us apply it to a full-chip design in reasonable CPU time. We validate our reduced model on several benchmark circuits against a detailed and highly accurate reference model. On average, the reduced model is within 16.4% of the reference model and is up to 38 times faster. Finally, we apply our methodology to a mixed-signal switch chip design consisting of 8 million gates and show that it finishes in 17 minutes.

# 1 Introduction

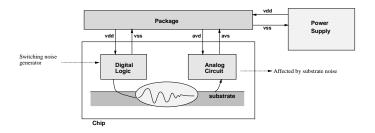

Mixed-signal designs have become ubiquitous with the proliferation of deep sub-micron (DSM) system-on-chip design methodologies. In such systems, maintaining signal integrity and reducing noise have become the most vexing issues. Switching noise due to large signal swings in the digital part can propagate through the common substrate and corrupt sensitive analog part (Figure 1). In technologies that have low resistivity substrates, noise generated in one region of the die may cause the rest of the chip to malfunction. Decreasing feature size lets more devices to be packed on a chip, generating higher overall noise. Smaller devices are also more sensitive to noise because of reduced noise margins. The increasing switching rates and decreasing transition times are also responsible for more transients. Due to all these DSM effects, substrate noise analysis (SNA) has become a critical problem in most mixed-signal designs.

The two major sources that contribute to substrate noise are transistor leakage currents and power supply noise (also called simultaneous switching noise). The junctions between wells and the substrate as well as between sources/drains and their respective wells form reverse-biased parasitic diodes. These diodes conduct small leakage currents, which are injected directly into the substrate. The second major source is the power supply noise and ground bounce. The switching inputs of the gates cause current to be drawn from the power supply network. Due to the resistance and inductance of the network, the potentials of the power supply and ground networks change, both spatially and temporally, resulting in power supply noise and ground bounce. Since substrate is connected to ground potential, the ground bounce is reflected as substrate noise. Out of these two sources, noise contributed by power supply and ground bounce is much greater than that by leakage current.

Figure 1: Substrate noise in mixed-signal system

Traditionally, SPICE was the primary tool used by designers for noise analysis. However, it is not feasible to use SPICE on even a 100K-gate block. It is important to come up with high level models and methods to enable chip-level analysis. Due to iterative nature of the existing design flows, substrate noise analysis must be very fast

Two important aspects of substrate noise are peak-to-peak noise and frequency-domain analysis. In this paper, we focus only on the peak-to-peak noise. The most important reason for doing this is that due to body effect, any fluctuation in substrate reference potential changes the threshold voltage of the devices, playing havoc with the noise margins. Analog devices are especially sensitive to substrate reference potential changes.

In this paper we present a full-chip substrate noise analysis methodology based on static timing analysis and reduced passive substrate noise models. The main contributions of our work are as follows.

- 1. We present a new pattern-independent methodology (PIM) for SNA. It does not use any testbench or simulation and is much faster as compared to the pattern-dependent flows used in the previous approaches [4, 5]. Our methodology is naturally suited to full-chip designs.

- 2. Our reduced model is based on sensitivity analysis, where we model more accurately the factors that influence substrate noise the most. We believe this is the first paper to use such an analysis technique for analyzing substrate noise.

- 3. We propose a current waveform generation technique which is novel in the context of noise analysis. It uses static timing analysis, circuit topology and cell functionality to derive the waveform corresponding to the worst case behavior.

- 4. Package influences the substrate noise considerably. We include the effect of package in our noise model.

- 5. Our methodology considers the influence of capacitive load driven by a gate in the circuit. This is in contrast with all previous works.

The outline of the paper is as follows. In the next section, we present a summary of the previous SNA work. Our proposed methodology is described in Section 3. In Section 4, we present a reference model, which will be used to validate the reduced model we propose. In Section 5, we present details of our methodology: namely the reduced model, the sensitivity analysis used in deriving it, and the algorithm used for current waveform modeling. Section

<sup>\*</sup>The work was done when the author was an intern at Fujitsu Laboratories of America.

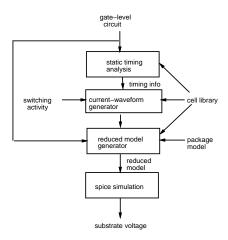

Figure 2: Pattern-independent methodology

6 presents experimental evidence of the accuracy of our proposed model and methodology. Section 7 describes how we apply the model to an industrial chip. Conclusions and directions for future work are presented in Section 8.

## 2 Previous Work

A lot of research work has been done on modeling the substrate noise during the design phase. [4, 13, 5, 6, 2] derive a passive network model that can be simulated with SPICE to yield substrate noise patterns for the entire design for the set of input vectors from a testbench. Each cell in the library is simulated with SPICE for all possible inputs and power supply current and substrate injection currents are extracted. This knowledge is used to do a full-chip analysis. One problem with [4, 13] is that they do not consider package inductance and the associated power supply noise, and hence are not very practical. [5, 6, 2] do not consider the dependency of noise on the load at each gate.

In [7] a time-series divided parasitic capacitance model is proposed for time-domain power supply current estimation. In [3] the authors give a comprehensive analysis of various device mechanics involved in the generation of substrate noise.

Note that all these approaches are input-pattern dependent, i.e., a separate model must be derived for each input pattern. Even for a moderately sized design, the number of models can become very large. This leads to exorbitant run-times, making these approaches impractical for a full chip analysis. Also, there is no guarantee that the maximum noise will be reported, since the worst-case input pattern may not be present in the testbench.

# 3 Proposed SNA Methodology

Our overall SNA methodology is shown in Figure 2. It is based on deriving a reduced model (RM) of the digital part of the design. First, a static timing analysis (STA) tool generates the timing information for each gate, such as the minimum and maximum rise/fall arrival and transition times. This, along with the switching activity information, is used by the current waveform generation (CWG) algorithm to construct the current waveform used in RM. The switching activities of various blocks in the design are expected to be provided by the designer; otherwise they may be deduced from a simulation testbench. The package model is also incorporated into RM. RM is simulated in SPICE to yield the substrate noise voltage.

Salient features of our methodology are as follows.

- RM consists of only passive components, and that too very few; so it can be simulated quickly. Also, RM does not include any explicit primary inputs and hence is input pattern-independent.

- The timing information of switching gates (such as signal arrival and transition times), which is an important determinant of

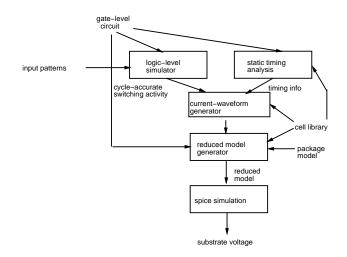

Figure 3: Pattern-dependent methodology

noise, is derived by invoking STA. STA implicitly captures the best and worst circuit timing behavior over all input patterns. We use the information relevant to model the worst case SN – the one that maximizes the peak-to-peak SN (see Section 5.3). The use of STA obviates the need for simulating the design over a large set of representative input patterns, and contributes to significant run-time improvement.

– Our methodology can handle a hierarchical design by composing the reduced models of different hierarchical components. The details are provided in Section 7.

– A pattern-dependent methodology (PDM), where a sequence of input vectors is provided, can be easily incorporated. This methodology, although impractical for a full chip design, can be used for a block-level design and should be more accurate than PIM. The PDM flow is shown in Figure 3. The sequence of input patterns is fed to a logic simulator, which yields derive cycle-accurate switching activity, i.e., for each cycle, lists of gates making rising or falling transitions. This information is used by the CWG algorithm, in that CWG in a given cycle is performed only for those gates that are switching in that cycle. Additionally, the arrival window, load capacitance and transition time information obtained from STA are also used.

#### 4 Reference Model

The reference model uses the transistor-level netlist for each cell in the design and augments it with a model for the substrate. The models for all cells are then composed to get the reference model for the design. This model serves as the standard with which we will compare our reduced models. Transistors are modeled in BSIM3. The substrate model is derived based on the following assumptions:

- The design is a standard cell CMOS design.

- The technology is NWELL with lightly doped P- epitaxial layer on top of a highly doped P+ substrate layer (BULK).

- The depth of the NWELL is assumed to be negligible compared to the thickness of the P+ epitaxial layer. Thus, the resistance of the NWELL is ignored.

- The BULK, due to its much lower resistivity compared to P- epi layer, is treated as one node for a given cell.

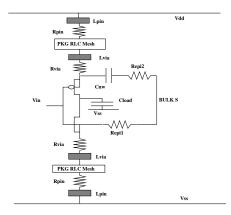

For simplicity, let us assume that the design consists of only one inverter. The corresponding reference model is shown in Figure 4. For a given cell, the model contains one substrate node referred to as BULK or substrate node S. The PMOS transistor substrate node is connected to the BULK node through a series connection of a capacitor  $C_{nw}$  and a resistor  $R_{epi2}$ . The capacitor  $C_{nw}$  represents the reverse-biased NWELL to P- epi layer junction diode and the resistor  $R_{epi2}$  represents the P- epi layer resistance under the NWELL area. For an NMOS transistor, its substrate node is

Figure 4: Reference model for an inverter

Figure 5: Reduced model

connected to S through a resistor  $R_{epi1}$  (the P- epi layer resistance under the transistor).

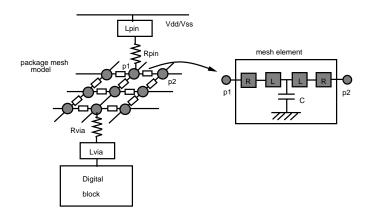

Each block has one VDD, one VSS and one BULK node. The VSS and VDD nodes are connected to a package model. The package modeling along with pin (Lpin, Rpin) and via (Lvia, Rvia) is described in more detail in Section 5.4. The substrate noise is measured at the BULK node point.

Previous work on reference substrate models includes [1, 14, 10, 11]. One drawback of these models is that they do not consider package model, which can be a big determinant in the noise.

# 5 Proposed Reduced Model

First, we present the basis of our reduced model in Section 5.1. For the model to be accurate and yet simple, we determine the minimum set of components that need to be modeled most accurately. We use sensitivity analysis (Section 5.2), which shows that current waveform and package model are the most important components, in that substrate noise is most sensitive to them. Their details are provided in Sections 5.3 and 5.4. In fact, modeling the current waveform is the core of our approach.

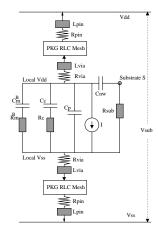

# 5.1 Original Reduced Model

Our reduced model for a digital block, as shown in Figure 5, is based on the model presented in [5]. It models switching activity and contains only passive circuit elements: a current source, internal capacitors and resistors. Capacitors and resistors model transistors, capacitance cells, and parasitics on the power/ground

Figure 6: Current Waveform

nets. We have enhanced the model in [5] by introducing the package RLC mesh,  $L_{via}$  &  $R_{via}$ , and  $L_{pin}$  &  $R_{pin}$ . The presence of only passive elements and that too in a small number ensure that circuit simulation is fast.

$R_m^B$  and  $C_m^B$  are the cumulative resistance and capacitance of transistors and wires in the block  $B.\ R_m^B$  is the average of pull-up and pull-down turn-on resistances of the transistors.  $C_m^B$  is the sum of all gate capacitances and wire loads in the block. For instance, for an inverter  $i,\ C_m^i$  is the load capacitance driven by i, which includes the gate capacitances of the fanout cells and the wire cap. If  $R_n$  and  $R_p$  are the ON resistances of the NMOS and PMOS transistors respectively,  $R_m^i=(R_n+R_p)/2$ . This assumes that the inverter is ON and OFF with equal probability, which is only an approximation. Also,  $R_n$  and  $R_p$  are functions of the operating point of the transistors. We approximate them by their average value in the linear region. As in [5], the equivalent single  $R_m^B$   $(C_m^B)$  value for the entire block B containing several cells is computed by assuming that  $R_m^i$ s  $(C_m^i$ s) of all cells i in B are connected in parallel.

$$\frac{1}{R_m^B} = \sum_i \frac{1}{R_m^i}; \quad C_m^B = \sum_i C_m^i$$

$C_c$  and  $R_c$  correspond to the decoupling capacitance cells placed in the vacant areas in the layout to guard against the voltage drop. They are computed from the SPICE netlists of these cells and the layout; the computation is similar to that of  $C_m$  and  $R_m$ .  $C_p$  is the parasitic capacitance on power or ground nets.  $R_{sub}$  is the pwell substrate resistance.  $C_{nw}$  is the junction capacitance between n-well and the substrate.  $R_{via}$  and  $L_{via}$  are the cumulative via resistance and inductance of the block.

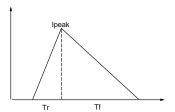

The current source, I, is due to the total power consumption of the block,  $P=VI_{avg}$ . Since the current waveform is modeled as a triangle, as shown in Fig 6,  $I_{avg}=\frac{1}{2}I_{peak}$   $(T_r+T_f)$  f, where f is the clock frequency.

#### 5.2 Sensitivity Analysis

RM approximates the behavior of a digital circuit that is relevant for SNA. To improve the accuracy of RM, the components in RM should be modeled as accurately as possible. As we use more accurate and hence complex models, the overall flow becomes slower and even intractable for large designs. Clearly, there is a trade-off between model accuracy and its scalability. Our approach is to determine the minimum set of parameters which have significant impact on substrate noise, and model them more accurately. For this purpose, we performed several sensitivity analysis experiments on both accurate and reduced models.

#### 5.2.1 Package Mesh

The package mesh is a two-dimensional mesh of RLC network representing the connection to off-chip pin. Table 1 shows the effect of 2D package mesh on the substrate noise for the reference model. As can be seen in this table, the noise is attenuated by the package mesh by a factor of 3. So it is important to model the package mesh accurately.

| block | SN with mesh (mV) | SN w/o mesh (mV) |

|-------|-------------------|------------------|

| A     | 26.4              | 88.2             |

| В     | 40.2              | 132.9            |

Table 1: Effect of package mesh

Figure 7: Variation of substrate noise with  $R_m \& C_m$

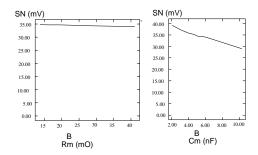

#### 5.2.2 Block Resistance and Capacitance

We performed several experiments on the effect of block resistance,  $R_m$ , and capacitance,  $C_m$ , on the substrate noise. Figure 7 shows the dependence of substrate noise on  $R_m$  and  $C_m$  variations. We can see that the effect of  $R_m$  variation on substrate noise is negligible. Varying  $R_m$  from 15 m $\Omega$  to 40 m $\Omega$  (i.e., by a factor of 2.7) changes the peak-to-peak noise from 34.8 mV to 34.0 mV (i.e., by a factor of 0.98). This result works to our advantage, since our  $R_m$  computation method is not very accurate (as mentioned in Section 5.1). Even if our  $R_m$  value is within a factor of 2.5 from the actual value, it should not affect SN.

The  $C_m$  variation has a somewhat larger impact on the noise, although still not very significant. Varying  $C_m$  from 2 nF to 10.2 nF (i.e., by a factor of 5) changes the noise almost linearly from 39.2 mV to 29.0 mV (a factor of 0.74).

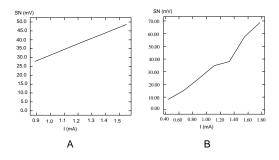

### 5.2.3 Current Waveform

In the original reduced model, the current waveform is assumed to have a triangular shape [5]. We performed two kinds of analyses. In the first, we changed the value of the peak current but kept  $T_r + T_f$  constant (Figure 8 A). In the second, we changed both peak current and  $(T_r + T_f)$ , but kept  $\frac{dI}{dt}$  constant (Figure 8 B). In both cases, the substrate noise is very sensitive to both the peak value and the shape of the current waveform.

#### 5.2.4 Conclusion

Based on the results of sensitivity analysis, we can conclude that substrate noise is not sensitive to  $R_m$  and only slightly sensitive to  $C_m$ . So, we need not model these two components too accurately. However, the noise is very sensitive to the package model and the

Figure 8: Variation of substrate noise with I: (A)  $T_r + T_f$  constant (B)  $\frac{dI}{dt}$  constant

current waveform. So, these two parameters must be modeled accurately. We describe their modeling schemes next.

## 5.3 Current Waveform Modeling

In the presented model, only the switching current is considered, i.e. the leakage and sub-threshold currents of transistors are ignored. The switching current is due to the charge and discharge of parasitic capacitances in the digital part of the circuit, when the transistors are making transitions. In this model, the switching current of a gate during the transition time is modeled as  $I(t) = \partial C(t) V_C(t)/\partial t$ . If we assume that the capacitance is constant during the transition time and  $V_C(t)$  is a ramp function from 0 to  $V_{DD}$  ( $V_{DD}$  to 0) for a rise (fall) transition, which are fair approximations, the current of a gate through its load capacitance is a pulse function with a peak value of  $I = CV_{DD}/\Delta T$  where  $\Delta T$  is the transition time. The pulse width is also  $\Delta T$ .

The overall current waveform is a superposition of the current pulses for all the gates in the digital part of the circuit.

In the presented approach, no logic simulation is performed. In other words, unlike the previous work in which there is a reduced model for each input pattern in the testbench [8, 6, 7, 13, 2, 9, 4], our model is independent of input patterns. As a result our pattern-independent model is several times faster than pattern-dependent methods. Our model is built by extracting information from STA and developing a reduced model that captures the worst case substrate noise over all possible input patterns.

The information obtained from STA for each gate g is as follows: 1. the arrival window: minimum arrival time  $T_{begin}^g$ , and maximum arrival time  $T_{end}^g$ , 2. the minimum transition time  $\Delta T_{min}^g$ , and 3. the maximum transition time  $\Delta T_{max}^g$

It is assumed that the transition start time,  $T_{tran}^g$ , lies anywhere in the arrival window. The main idea of our proposed approach is to assign a valid transition start time for each gate g (i.e.,  $T_{begin}^g \leq T_{tran}^g \leq T_{end}^g$ ), such that the peak current and, as a result the substrate noise, are maximized.

Since no logic simulation is performed in the presented methodology to precisely determine which gates are making transition in each direction (rising or falling), switching activity and the relative number of gates making rising and falling transitions are assumed to be known. This information can be obtained either directly from the designer or from the logic simulation dump generated during design validation.

Figure 9 shows the pseudo code for the overlapping algorithm which finds the worst-case maximum possible peak current based on the arrival window, transition time, and load capacitance for each gate obtained from static timing analysis. This algorithm not only finds the maximum peak current, but also constructs the entire current waveform. In each iteration (lines 5-16), the maximum peak current that is possible from the remaining unselected gates (i.e., in list L) is computed. This is done as follows. For each gate  $g_i$ ,  $I_{peak}^i$ , the maximum current that can be drawn at the start point of its arrival window,  $T_{begin}^{gi}$ , is computed (lines 6-11). This is done by adding up the currents due to all gates  $g_j$  whose arrival windows overlap with the arrival window of  $g_i$ . Then, the gate  $g_k$  with overlap with the arrival window of  $g_i$ . Then, the gate  $g_k$  with maximum current is determined (lines 12-13). The transition start times for all the gates contributing to this maximum current (i.e., those in the list  $L_k$ ) are set to the start point in the arrival window of  $g_k$ . These gates are removed from the list L (lines 14-16). The above iteration is performed until the list L becomes empty, i.e. the entire current waveform is constructed.

The above procedure is invoked once for the gates making rising transition and once for those making falling transition. In actual implementation of this algorithm, the list is sorted based on the start point of the arrival windows of the gates. The search for the gates which are overlapping with a given gate is stopped if the difference in start points is more than the largest arrival window in the circuit. Using these optimizations, the overall complexity of this algorithm is  $O(n^2 \log n)$ , where n is the total number of gates in the design.

```

1.L \leftarrow \text{list of all switching gates}

2.for each gate g_i \in L do

I^{g_i} \leftarrow C_{g_i} V_{DD} / \Delta T^{g_i}

4.repeat

for each gate g_i \in L do

I_{peak}^i \leftarrow I^{g_i}

L_i \leftarrow \{g_i\}

for each gate g_j \in L(j \neq i) do

if \ T_{begin}^{g_i} \leq T_{begin}^{g_j} \leq T_{end}^{g_i} \text{ then}

I_{peak}^i \leftarrow I_{peak}^i + I^{g_j}

L_i \leftarrow L_i \cup \{g_j\}

I_{peak} \leftarrow \max_i \{I_{peak}^i\}

k \leftarrow \arg\max_i \{I_{peak}^i\}

for each gate g_i \in L_k do

T_{tran}^{g_i} \leftarrow T_{begin}^{g_k}

L \leftarrow L - L_k

L = \Phi

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

17.until L = \Phi

```

Figure 9: The overlapping algorithm for generating maximum peak current

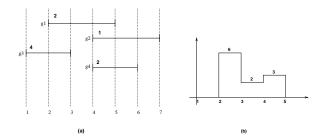

Figure 10: Example: (a) arrival time windows of gates  $g_1$  to  $g_4$ ; (b) current waveform using CWG algorithm

We illustrate the algorithm with the help of an example. Figure 10.a shows the arrival time windows of gates  $g_i$ , i=1 to 4, along with the current values  $I^{g_i}$ . For instance,  $T^{g_1}_{begin}=2$ ,  $T^{g_1}_{end}=5$ ,  $I^{g_1}=2$ . The maximum current at time 1, start point for  $g_3$ , is 4 units; at time 2, start point for  $g_1$ , is 6 units; and at time 4, start point for  $g_2$  and  $g_4$ , is 5 units. Hence, the maximum current is 6 units, and the transition start time for  $g_1$  and  $g_3$  is set to time 2.  $g_1$  and  $g_3$  are removed from the list. The next maximum happens at time 4 for  $g_2$  and  $g_4$ . Note that the overall current waveform is obtained by superimposing current pulses for all the gates. The duration of current pulse for a gate is equal to the minimum transition time of that gate; this takes care of the worst-case condition. Assume that the minimum transition time for  $g_1$  is 2 units and for  $g_2$ ,  $g_3$  and  $g_4$  1 unit each. The overall current waveform for this example is shown in Figure 10 b.

### 5.4 Package Model

Package model is an abstraction of power and ground planes in the package. It has a large impact on the power supply noise, because package inductance directly affects the  $L\frac{\mathrm{d}i}{\mathrm{d}t}$  noise [12]. We model the package as an RLC mesh (Figure 11). The inductance L, sheet resistance R, and capacitance C are computed from layer information. The package model is connected to VDD/VSS through  $L_{pin}$  &  $R_{pin}$  and to the digital part through  $L_{via}$  &  $R_{via}$ .

Figure 11: Mesh model of the package

# 6 Reduced Model Validation

The reduced model presented above was validated against the reference model. Since reference models for large circuits cannot be simulated due to exorbitant CPU-times, the reduced model can only be validated for relatively small circuits. Several circuits were generated with sizes varying from 50 to 700 gates. In these experiments, the technology is 0.11- $\mu$ , with VDD = 1.2V.

The results for the pattern-independent methodology (PIM) are presented. The reference model for each circuit was simulated with a testbench which had less than 10 vectors. The peak-to-peak substrate voltage over the entire testbench was measured. For PIM, the current waveform and the reduced model were generated based on the timing windows obtained from a static timing analysis tool, as described in Section 5. The switching ratios used to generate the reduced model were calculated from the testbench used in the reference model. The reduced model was simulated and peak-to-peak substrate noise voltage measured.

Table 2 shows results of the peak-to-peak substrate noise voltage comparisons. The noise measured using the reduced model in the pattern-independent flow is close to that measured by the reference model: on average the difference is 16.4%. However, there is a dramatic improvement in the CPU time, which is the total time for generating the model and simulating it. The PIM is 17.8 times faster on average and for c6 and c7, more than 30 times faster. Note that the CPU time for the reference model increases linearly with the number of cycles. In our experiments, the reference model was simulated for a very small number of cycles. Larger designs need exponentially more cycles, especially if the worst- or near-worst-case noise patterns are to be captured. Correspondingly, CPU times for the reference model simulation increase exponentially. However, for PIM, the time grows linearly with the design size, since model generation time is linear in the design size. The simulation time does not depend on the number of input patterns. Therefore, the speedup using our methodology will be even higher for large designs.

# 7 Chip-level SNA

### 7.1 Chip-level Analysis Flow

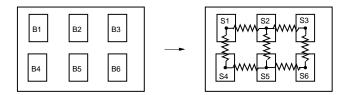

For a chip-level design, it is not possible to measure the the substrate noise by a detailed SPICE model. We use the following methodology to handle the chip complexity. It exploits the hierarchical nature of the design. It takes three inputs: design information, cell libraries and technology parameters. Design information consists of gate netlist, chip floorplan, package size and parameters. Cell libraries include timing libraries and SPICE models. Technology parameters include process information such as sheet resistances of metal layers, capacitance, etc. The output is the substrate noise level for each hierarchical block.

The main steps of the methodology are as follows. First, the reduced model  $M_i$  of each block  $B_i$  is derived, as described in Sec-

| $\operatorname{ckt}$ | gate                 | Noise (mV)           |             |       | CPU Times (secs)     |                      |      |

|----------------------|----------------------|----------------------|-------------|-------|----------------------|----------------------|------|

|                      | $\operatorname{cnt}$ | $\operatorname{ref}$ | $_{ m red}$ | %err  | $\operatorname{ref}$ | $\operatorname{red}$ | X    |

| c1                   | 137                  | 12.4                 | 10.9        | -12.0 | 785                  | 87                   | 9.0  |

| c2                   | 281                  | 22.9                 | 16.1        | -29.8 | 1778                 | 89                   | 20.0 |

| c3                   | 57                   | 3.9                  | 3.3         | -15.6 | 349                  | 76                   | 4.6  |

| c4                   | 99                   | 7.6                  | 6.6         | -13.0 | 538                  | 85                   | 6.3  |

| c5                   | 224                  | 11.2                 | 11.8        | 5.2   | 1339                 | 88                   | 15.2 |

| c6                   | 701                  | 42.6                 | 39.3        | -7.9  | 2525                 | 81                   | 31.2 |

| c7                   | 464                  | 18.7                 | 24.5        | 31.0  | 3660                 | 95                   | 38.5 |

| avg                  |                      |                      |             | 16.4  |                      |                      | 17.8 |

ref: peak-to-peak substrate noise for reference model red: peak-to-peak substrate noise for reduced model err = (red - ref)/ref; X: CPU time speed-up

Table 2: Substrate noise results

Figure 12: Floorplan-driven, hierarchical SN model

tion 5. Let the substrate in each block  $B_i$  be  $S_i$  (Figure 12). The reduced block models are then composed to generate a single chiplevel model M with power structure representation. The relative placement of the blocks in the floorplan is used to derive M. If blocks  $B_i$  and  $B_j$  are physically adjacent in the floorplan, their corresponding substrate nodes  $S_i$  and  $S_j$  are connected through a resistor  $R_{ij}$ . The value of  $R_{ij}$  is computed using the sizes of the blocks and sheet resistance of the bulk. After combining the composed model with the package model, SPICE simulation is performed and SN is measured for each block.

## 7.2 Application to A Chip-level Design

We applied our methodology to a mixed-signal, switch chip. The analog components of this chip are the high-speed I/O macros. The gate count is 8 million. The chip has 34 top-level blocks, each block consisting of hundreds of thousands of gates. In our modeling, we were only concerned about P2P SN. The designers provided us with the switching activity for each block. The results were as follows. The complete simulation finished in 17 minutes. The maximum value of P2P SN over all  $S_i$  nodes was 40.7mV, the average being 34.5mV. The designers had specified a threshold of 60mV, which was met.

### 8 Conclusions

We presented a pattern-independent methodology for measuring peak-to-peak substrate noise of a mixed-signal design. The key idea is to derive a reduced model consisting only of the smallest possible number of passive components. Based on sensitivity analysis, we determined that the noise is most sensitive to the current waveform. Unlike the previous work, in which a pattern-dependent reduced model is derived and evaluated for each input pattern, the proposed reduced model is generated and evaluated only once. The proposed model is validated on several benchmark circuits against the accurate reference model. The reduced model is within 16.4% of the reference model with respect to the peak-to-peak noise value and up to 38 times faster. The speed-up will be even more impressive for larger designs. Finally, a technique for measuring the

substrate noise of a hierarchical full-chip design was proposed and the results for a real chip were presented.

The future work is in the following directions. For a few circuits, such as c2 and c7 in Table 2, the noise difference is about 30%. We will like to reduce the gap. Also, currently, the reduced model can yield smaller noise values than the reference model, which is not desirable. We believe that these issues can be handled by modeling the current waveform more accurately. For instance, circuit topology and logic implications are being integrated in the CWG algorithm. Also, we need better modeling of the current waveform in the presence of the package inductance. Not only is the peak value of the current waveform important, but also the slope due to  $L\ dI/dt\ drop$ . Finally, in this paper, we focused only on the peak-to-peak noise in the time domain, since the analog part of the chip we targeted consisted only of I/O macros. For a design that uses frequency-sensitive analog components, our model should be extended to handle frequency analysis.

## References

- Edgar F. M. Albuquerque and Manuel M. Silva. Evaluation of Substrate Noise in CMOS and Low-Power Logic Cells. In ISCAS, 2001.

- [2] M. Badaroglu, M. Heijningen, V. Gravot, S. Donnay, H. J. DeMan, G.E. Gielen, M. Engles, and I. Bolsens. High-level simulation of substrate noise generation from Large Digital Circuits with Multiple Supplies. In *DATE*, 2001.

- [3] J. Briaire and K. S. Krisch. Principles of Substrate Crosstalk Generation in CMOS Circuits. In TRANSCAD, volume 19 NO. 6, Jun 2000.

- [4] E. Charbon, P. Miliozzi, L. P. Carloni, A. Ferrari, and A. Sangiovanni-Vincentelli. Modeling Digital Substrate Noise Injection in Mixed-Signal IC's. In TRANSCAD, volume 18 NO. 3, Mar 1999.

- [5] M. Heijningen, M. Badaroglu, S. Donnay, M. Engles, and I. Bolsens. High-Level Simulation of Substrate Noise Generation Including Power Supply Noise Coupling. In DAC, 2000.

- [6] M. Heijningen, M. Badaroglu, S. Donnay, G.E. Gielen, and H. J. DeMan. Substrate Noise Generation in Complex Digital Systesm: Efficient Modeling and Simulation Methodology and Experimental Verification. In *IEEE JSSC*, 2002.

- [7] M. Nagata, T. Morie, and A. Iwata. Modeling Substrate Noise Generation in CMOS Digital Integrated Circuits. In CICC, 2002.

- [8] M. Nagata, Y. Murasaka, Y. Nishimori, T. Morie, and A. Iwata. Substrate Noise Analysis with Compact Digital Noise Injection and Substrate Models. In *Int'l Conf. on VLSI Design*, 2002.

- [9] M. Nagata, T. Ohmoto, Y. Murasaka, T. Morie, and Atsushi Iwata. Effect of Power-Supply Parasitic Components on Substrate Noise Generation in Large-Scale Digital Circuits. In Symp. on VLSI Circuits, 2001.

- [10] D. Ozis, K. Mayaram, and T. Fiez. An Efficient Modeling Approach for Subsrate Noise Coupling Analysis. In ISCAS, 2002.

- [11] A. Samavedam, A. Sadate, K. Mayaram, and T. Fiez. A Scalable Substrate Noise Coupling Model for Design of Mixed-Signal IC's. In *IEEE JSSC*, 2000.

- [12] N. K. Verghese, T. J. Schmerbeck, and Allstot D. J. Simulation Techniques and Solutions for Mixed-signal Coupling in Integrated Circuits. In Kluwer Academic Publishers, 1995.

- [13] S. Zanella, A. Neviani, E. Zanoni, P. Miliozzi, E. Charbon, C. Guardiani, L. P. Carloni, and A. Sangiovanni-Vincentelli. Modeling of Substrate Noise Injected by Digital Libraries. In ISQED, 2001.

- [14] Y. Zinzius, E. Lauwers, G. Gielen, and W. Sansen. Evaluation of The Substrate Noise Effect On Analog Circuits in Mixed-Signal Designs. In Southwest Symp. on Mixed-signal Designs, 2000.