# Structural Testing on Real Boards

Peter Bach and Michael Bosch

Universität des Saarlandes 66041 Saarbrücken, Germany, {pb,hirbli}@cs.uni-sb.de

## **1** Introduction

For structural interconnect testing a graph is generated from the physical layout of the interconnects. The vertices are then colored. The number of colors determines the number of different serial test patterns needed. Based on real PCB layout data we give experimental results, that show how the choice of the graph generation method and of the coloring algorithm influence the number of colors.

### 2 Graph Generation

Usually, faults on PCBs are not distributed equally. They appear more often on outer layers than on inner layers due to soldering and handling. Faults between nets on the same layer and adjacent layers are more frequent than faults between nets on remote layers. The following equations define sets of layer pairs for outer layers  $(LP_O = \{(1, 1), (L, L)\})$ , same layers  $(LP_S\{(l, l) : l = 2, ..., L - 1\})$ , adjacent layers  $(LP_A = \{(l_1, l_2) : |l_1 - l_2| = 1\})$  and all other layer pairs  $(LP_X = \{(l_1, l_2) : |l_1 - l_2| > 1\})$ . We define the distance of two nets u and v by one distance values per set of layers: For  $* \in \{O, S, A, X\}$  we define

$$\Delta_*(u, v) = \min\{\delta(s, t) : s \in \operatorname{seg}(u), t \in \operatorname{seg}(v), \\ (l(s), l(t)) \in LP_*\}.$$

$\delta(s, t)$  is the two dimensional Euclidean distance between segment s of net u and segment t of net v. The layer number  $1 \leq l(s) \leq L$  indicates which layer segment s is located on. The definition of graph G = (V, E)depends on the four parameters  $\epsilon_*$ :

$$(u,v) \in E \iff \exists * \in \{O, S, A, X\} : \Delta_*(u,v) \le \epsilon_*$$

The parameters  $\epsilon_*$  determine the maximum extent a fault may have.

### **3** Measurements

We applied the presented graph generation to six different PCBs from the SB-PRAM [2] parallel computer project. For our measurements we used the coloring algorithms GREEDY, DSATUR and MAXIS from [1].

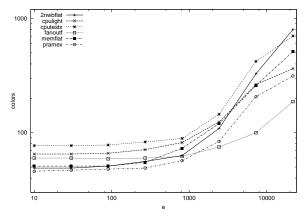

We made measurements with all combinations of parameters (PCB,  $\epsilon_*$ , coloring algorithm). Figure 1 shows the number of colors needed by the best coloring algorithm versus  $\epsilon_O$  for the different boards.

Two main results can be derived from the measurements: First, choosing physically reasonable values for  $\epsilon_*$ , the number of serial test vectors needed can be reduced by more than an order of magnitude. Second, the DSATUR algorithm performs best in most cases.

Figure 1: minimal colors ( $e = \epsilon_O$ )

#### References

- Joseph Culberson. Graph coloring programs. http://www.cs.ualberta.ca/~joe/Coloring/Colorsrc/, October 1997.

- [2] SB-PRAM web page. http://www-wjp.cs.unisb.de/projects/sbpram/, January 2000.