## ADVANCE PROGRAMME

www.date-conference.com

Design, Automation and Test in Europe

March 19-23, 2018, Dresden, Germany

## DATE 2018 SPONSORS

European Design and Automation Association

Electronic System Design (ESD) Alliance

IEEE Council on Electronic Design Automation

ACM Special Interest Group on Design Automation European Electronic Chips & Systems design Initiative

Russian Academy of Sciences

## TECHNICAL CO-SPONSORS

- IEEE Computer Society test technology technical Council (tttC)

- IEEE Solid-State Circuits Society (SSCS)

- International Federation for Information Processing (IFIP)

## **EVENT SPONSORS**

Supported by the City of Dresden

## CORPORATE SPONSORS

## PROGRAMME GUIDE

| Media Partners                                                    | 002        |

|-------------------------------------------------------------------|------------|

| Welcome                                                           | 004        |

| General Information                                               | 011        |

| KEYNOTE SPEAKERS                                                  |            |

| Amnon Shashua, Mobileye   Intel Corporation, US                   | 006        |

| Christopher Voigt, MIT, US                                        | 007        |

| Jelena Vuckovic, Stanford University, US                          | 008        |

| Thomas Form, Volkswagen AG, DE                                    | 009        |

| EXECUTIVE SESSIONS                                                | 015        |

| Giovanni De Micheli, EPFL, CH                                     |            |

| Marco Casale-Rossi, Synopsys, IT                                  |            |

| FUTURE AND EMERGING TECHNOLOGIES                                  | 016        |

| Robert Wille, Johannes Kepler University Linz, DE                 |            |

| Subhasish Mitra, Standford University, US                         |            |

| DESIGNING AUTONOMOUS SYSTEMS                                      | 017        |

| Rolf Ernst, Institut für Datentechnik und Kommunikationsnetze, DE |            |

| Marco Platzner, University of Paderborn, DE                       |            |

| SPECIAL & EU SESSIONS                                             | 018        |

| Giovanni De Micheli, EPFL, CH   Marco Casale-Rossi, Synopsys, IT  |            |

| Paul Pop, Technical University of Denmark, DK                     |            |

| DATE 2018 – AT A GLANCE                                           | 021        |

| A brief overview of the event                                     |            |

| MONDAY TUTORIALS AND EVENTS                                       | 029        |

| Seven afternoon tutorials                                         | 029        |

| Forum: Advancing Diversity in EDA                                 | 138        |

| 2nd IoT Student Challenge, sponsored by IEEE CEDA and             |            |

| Texas Instruments                                                 | 021        |

| TECHNICAL SESSIONS                                                | 040        |

| Full listing of DATE technical programme, special sessions        |            |

| FRIDAY WORKSHOPS                                                  | 104        |

| Six full-day workshops                                            |            |

| EXHIBITION THEATRE PROGRAMME OVERVIEW                             | 120        |

| Free for exhibition visitors                                      |            |

| UNIVERSITY BOOTH                                                  | 122        |

|                                                                   |            |

| FRINGE TECHNICAL MEETINGS                                         | 138        |

|                                                                   |            |

| CO-LOCATED WORKSHOPS                                              | 141        |

| EXHIBITION GUIDE                                                  | 143        |

|                                                                   |            |

| Committees & Topic Chairs<br>Detailed Index                       | 167<br>173 |

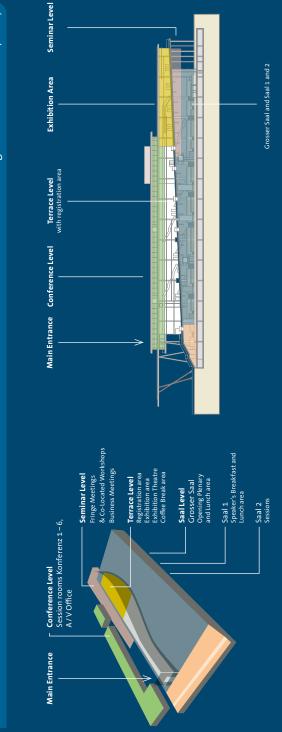

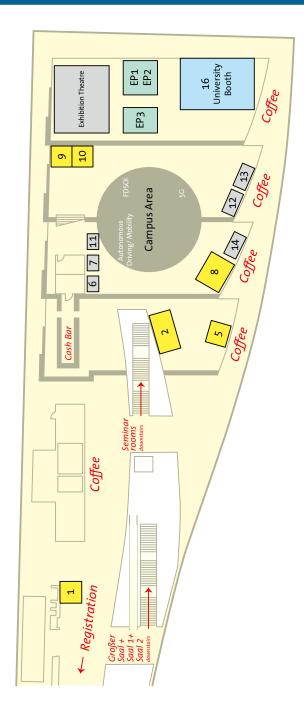

| Venue Plan                                                        | C04        |

|                                                                   | -          |

## MEDIA PARTNERS

The DATE organisation and sponsors would like to extend their warmest gratitude to all press journalists who give DATE coverage in the editorial pages. Listed below are the media houses and publications who generously agree to form a media partnership with DATE, and whose publications can be found on-site.

#### **AUTOCAD & Inventor MAGAZIN**

AutoCAD & Inventor Magazin covers more than just IT subjects – we report on all aspects of professional life that are important for constructing engineers and planners. We focus especially on innovations in drive technology, automation technology, connectivity, construction components, fluid technology, electrical engineering and materials.

www.autocad-magazin.de

## Chip Design Magazine

Chip Design covers all of the technical challenges and implementation options engineers face in the development and manufacture of today's complex integrated circuits. Chip Design is the only media network dedicated to the advanced IC Design market. Visit www.chip-designmag.com to stay informed about the latest developments in chip modeling, architecture, design, test and manufacture, from EDA tools to digital and analog hardware issues. The System Level Design and Low Power Engineering Portals offer focused editorial content you won't want to miss. And, be sure to visit www.eecatalog.com for valuable information about all of Extension Media's outstanding technology resources.

www.chipdesignmag.com

#### **EDACafé**

EDACafe.com is the #1 EDA web portal. Thousands of IC, FPGA and System designers visit EDACafé.com to learn the latest news and research design tools and services. The sites attract more than 75,000 unique visitors each month and leverages TechJobsCafé.com to bring you job opportunities targeted to engineering and design. And daily e-newsletters reach more than 40,000 engineering professionals.

For more details visit www.EDACafe.com and www.TechJobsCafe.com

## Engineering & Technology Magazine – Published by The IET

Engineering & Technology is packed with articles on the latest technology covering the areas of communications, control, consumer technology, electronics, IT, manufacturing & power engineering. It is

#### MEDIA PARTNERS

Europe's largest circulation engineering magazine, published monthly & offers a global circulation of over 140,000 copies to more than 100 countries & a high pass-on readership.

Each member of the Institution of Engineering & Technology (IET) receives a copy as part of their membership package. Readers include design & development engineers, system designers & integrators, solutions providers & installers, engineering distributors, consultants, planners, facilities managers & end-users.

With its HQ in London & regional offices in Europe, North America & Asia-Pacific, the Institution of Engineering & Technology provides a global knowledge network to facilitate the exchange of ideas & promote the positive role of technology around the World. The Institution of Electrical Engineers, dating from 1889, became the Institution of Engineering & Technology in 2006. It now organises more than 120 conferences & other events each year whilst providing professional advice & briefings to industry, education & governments.

#### www.eandtmagazine.com

## Elektronik i Norden

Elektronik i Norden, an important tool for the Nordic electronic industry. We want Elektronik i Norden to be the most important source of information for the Nordic electronic industry (Sweden, Finland, Norway and Denmark). A circulation of 25,800 personally addressed copies proves we are the major electronics paper in this area. We publish news, comments and in-depth technical articles.

#### www.elinor.se

## Semicon Europa 2018

## The Strongest Single Event for Electronics Manufacturing in Europe

13-16 November, 2018

SEMICON Europa 2018 events, co-located with electronica, will expand attendee opportunities to exchange ideas and promote technological progress featuring the most advanced and innovative electronics manufacturing platform in Europe.

The high turnout at SEMICON Europa and electronica – 13-16 November 2018 at Messe München, Munich, Germany – demonstrates the growing importance of business networking and global cross-collaboration, supporting SEMI mantra of "Connect, Collaborate, and Innovate."

Europe is strategically positioned in the global electronics supply chain to enable SMART applications as strong investment in its semiconductor industry continues.

Plan now to attend! Claim your place at the Largest Microelectronics Event in Europe.

Thinking about becoming a Sponsor? Contact SEMI Europe Sales: Ms. Denada Hodaj at dhodaj@semi.org

#### www.semiconeuropa.org

## WELCOME TO DATE 2018

## Dear Colleague,

We proudly present the Advance Programme of **DATE 2018**. DATE combines the world's favourite electronic systems design and test conference with an international exhibition for electronic design, automation and test, from system-level hardware and software implementation right down to integrated circuit design.

Out of a total of 766 paper submissions received, a large share (39%) has come from authors in Europe, 26% of submissions are from America, 34% from Asia, and 1% from the rest of the world. This distribution clearly demonstrates DATE's international character, global reach, and impact.

For the 21st successive year, DATE has prepared an exciting technical programme. With the help of 335 members of the Technical Program Committee who carried out 3079 reviews (mostly four reviews per submission), finally 185 papers (24%) were selected for regular presentation and 85 additional ones (cumulatively 35%, including all papers) for interactive presentation.

The DATE conference takes place from 19 to 23 March 2018, at the International Congress Center Dresden, Germany. On the first day of the DATE event, four in-depth technical tutorials on the four main topics of DATE as well as three industry hands-on tutorials are given by leading experts in their respective fields. Technical topics covered are emerging technologies for computing, industrial internet-of-things (IoT), reliability from physics to CAD, virtual prototyping and low-power design, as well as industrial topics on building ARM powered IoT, computer vision for automated driving in MATLAB, and how to implement domain-specific modeling languages.

Also on Monday, DATE hosts the first edition of a new forum, "Advancing Diversity in Electronic Design Automation (DivEDA)", which aims to increase the number and visibility of women and underrepresented minorities in the research community.

The **plenary keynote speakers** on **Tuesday** are Prof. Amnon Shashua, CEO & CTO of Mobileye, whose talk is about "The Responsibility Sensitive Safety (RSS) Formal Model toward Safety Guarantees for Autonomous Vehicles" and Dr. Christopher Voigt, Professor of Biological Engineering at MIT, to talk about "Programming Living Cells: Design Automation to Map Circuits to DNA". On the same day, the **Executive Track** offers a series of business panels with executive speakers from companies leading the design and automation industry, discussing hot topics.

The main conference programme from Tuesday to Thursday includes 79 technical sessions organized in parallel tracks from the four areas

- D Design Methods & Tools

- A Application Design

- T Test, Reliability, and Robustness

- E Embedded and Cyber-Physical Systems

and from several special sessions on hot topics, such as emerging technologies, low power challenges and approximate computing for IoT devices, security-aware design in cyber-physical systems, new benchmarking methods and applications for emerging devices, circuits, and architectures, methodologies to design and manage exascale computing system technologies, as well as results and lessons learned from European projects.

## WELCOME TO DATE 2018

Jan Madsen

Ayse K. Coskun

Two Special Days in the programme focus on areas bringing new challenges to the system design community: Future and Emerging Technologies and Designing Autonomous Systems. Each of the special days has a full programme of keynotes, panels, tutorials and technical presentations.

During the Special Day on "Future and Emerging Technologies" on Wednesday, a keynote is given by Prof. Jelena Vuckovic from Stanford University, on "From Inverse Design to Implementation of Robust and Efficient Photonics for Computing". On Thursday in the frame of the Special Day on "Designing Autonomous Systems", Thomas Form, Head of Electronics and Vehicle Research, Volkswagen AG, and co-ordinator of the Pegasus research project on safety of automated driving gives a talk about "Autonomous Driving: Ready to Market? Which are the Remaining Top Challenges?".

Additionally, there are numerous Interactive Presentations which are organized into five IP sessions.

To inform attendees on commercial and design-related topics, the Exhibition Theatre provides a full programme, combining presentations by exhibiting companies, best-practice reports by industry leaders on their latest design projects and interviews with keynote speakers form the conference. The conference is complemented by an exhibition, running for three days (Tuesday - Thursday), including campus booths with focus on special topics such as autonomous driving, 5G, FDSOI and IoT Security. The exhibition provides a unique networking opportunity and sets the perfect venue for industry to meet university professors to foster their university programme and also for PhD Students to meet future potential employers.

On Friday, there are 6 full-day workshops, covering a large number of hot topics like software for IoT, emerging memories and interconnects, and new platforms for future cars.

We wish you an exciting and memorable DATE 2018, a successful exhibition visit and an entertaining DATE party on Wednesday evening which takes place in the "Deutsches Hygiene-Museum Dresden".

DATE 2018 General Chair Jan Madsen

**Technical University** of Denmark, DK

DATE 2018 Programme Chair

Ayse K. Coskun Boston University, US 1.1.1

## TUESDAY OPENING CEREMONY

**Amnon Shashua**

March 20, 2018, 0915 - 1000, Großer Saal

The Responsibility Sensitive Safety (RSS)

Formal Model toward Safety Guarantees for

Autonomous Vehicles

**Prof. Amnon Shashua,** CEO & CTO, Mobileye, an Intel company, and Senior Vice President, Intel Corporation, US

In recent years, car makers and tech companies are racing toward self-driving cars. A critical component in getting society acceptance to the technology is to find a way to guarantee safety. The prevailing common wisdom is a data-driven empirical approach for safety validation where the more mileage driven the better the maturity of the system must be. I will describe a model in which the sources of errors due to Planning (the actions and decisions for negotiating motion in traffic) can be fenced out from the data driven approach through a formal model of the common sense behind human judgment of what it means to cause an accident and how to define actions that will guarantee that the AV will never cause an accident due to Planning. The model creates a clear distinction of what can be certified by regulators and what should be left to the judgment of AV manufacturers. The RSS model also puts in context the conversation of "ethical dilemmas" by providing a formal framework for the discussion.

**Christopher Voigt**

March 20, 2018, 1000 - 1030, Großer Saal

1.1.2

## Programming Living Cells: Design Automation to Map Circuits to DNA

Christopher Voigt, Professor of Biological Engineering at MIT, US

Platforms are being established to facilitate large genetic engineering projects. A desired cellular function is divided into systems that can be developed independently and then combined. Genetic sensors allow cells to receive environmental and cell state information. Sensory information is integrated by genetic circuits, which control the conditions and timing of a response. The circuit outputs are connected to actuators that control what the cell is doing, from building molecules to moving and communicating. Design automation tools from the electronics industry are applied to map a circuit design to a DNA sequence. Collectively, this enables a wide range of applications, for example cells that communicate to build a material, navigate the human body to treat a disease, or protect plants by responding to the environment.

7.0

## WEDNESDAY KEYNOTE ADDRESS

Jelena Vuckovic

March 21, 2018, 1350 – 1420, Saal 2 Supported by IEEE CEDA

From Inverse Design to Implementation of Robust and Efficient Photonics for Computing

Jelena Vuckovic, Stanford University, US

It is estimated that nearly 10% of the world electricity is consumed in information processing and computing, including data centers [D.A.B. Miller, Journal of Lightwave Technology, 2017]. It is clear that the exponential growth in use of these technologies is not sustainable unless dramatic changes are made to computing hardware, in order to increase its speed and energy efficiency. Optical interconnects are considered a solution to these obstacles, with potential to reduce energy consumption in on-chip optical interconnects to atto-Joule per bit (aJ/bit), while increasing operating speed beyond 20GHz. However, the state of the art photonics is bulky, inefficient, sensitive to environment, lossy, and its performance is severely degraded in real-world environment as opposed to ideal laboratory conditions, which has prevented from using it in many practical applications, including interconnects. Therefore, it is clear that new approaches for implementing photonics are crucial.

We have recently developed a computational approach to inverse-design photonics based on desired performance, with fabrication constraints and structure robustness incorporated in design process. Our approach performs physics guided search through the full parameter space until the optimal solution is reached. Resulting device designs are non-intuitive, but are fabricable using standard techniques, resistant to temperature variations of hundreds of degrees, typical fabrication errors, and they outperform state of the art counterparts by many orders of magnitide in footprint, efficiency and stability. This is completely different from conventional approach to design photonics, which is almost always performed by brute-force or intuition-guided tuning of a few parameters of known structures, until satisfactory performance is achieved, and which almost always leads to sub-optimal designs.

Apart from integrated photonics, our approach is also applicable to any other optical and quantum optical devices and systems.

From 1345 - 1350, there will be the Presentation of the IEEE TCCPS Technical Achievement Award to Prof. Alberto Sangiovanni-Vincentelli (handed over by Shiyan Hu, Chair of TCCPS) directly before the start of the keynote address.

## THURSDAY KEYNOTE ADDRESS

Thomas Form

March 22, 2018, 1320 - 1350, Saal 2

11.0

## Autonomous Driving: Ready to Market? Which are the Remaining Top Challenges?

**Thomas Form,** Head of Electronics and Vehicle Research, Volkswagen AG, and co-ordinator of the Pegasus research project on safety of automated driving

During the last years a lot of prototypes for automated/autonomous driving vehicles have been presented to the public. Depending on the use case car manufacturers or tech companies have used an evolutionary or a revolutionary approach. While the evolutionary way should be more reasonable applied for owned cars due to cost restraints and the need for the functionality to work more or less by "something everywhere", the revolutionary approach following the strategy "everything somewhere" seems to be the better solution for fleets of autonomous cabs or shuttles.

Although we have seen a lot of functional concepts for both approaches to automation, there are still some big challenges to be solved. On one hand the whole automation function has to be designed redundantly to ensure a sufficient functional safety level. In this context the use of Artificial Intelligence based networks could be a solution in particular neuronal networks based on deep learning.

On the other hand there is still the question "how good is good enough" having in mind that perfectly working systems cannot be realized and how can the necessary verification/validation process be implemented. The public funded project PEGASUS is working to provide first answers.

However: do we have considered all impacts of automated mobility?

Association & Conference Management Group

# K.I.T. Group

With more than 25 years of expertise in the organisation of conferences and strategic alliances, we are now based in Germany with Europe at our feet and operational offices worldwide. Over 2,500 congresses, organised across 5 continents, from 50 to 28,000 participants!

We can be everywhere for you!

K.I.T. Group GmbH Dresden Bautzner Straße 117–119 01099 Dresden

www.kit-group.org

Phone +49 351 4967540 Fax +49 351 4956116 info@kitdresden.de

#### GENERAL INFORMATION

This printed programme is intended to provide delegates with an easy reference document during their attendance at DATE 2018. Full conference information including all technical programme details, information on awards, conference registration costs, information about accommodation, travel offers and social events is available on the conference website www.date-conference.com

## **Dates and Venue**

The conference will take place from 19 to 23 March, 2018, in the MAR-ITIM Hotel & International Congress Center Dresden (ICCD).

Maritim Hotel & Internationales Congress Center Dresden Ostra-Ufer 2 / Devrientstr. 10 – 12 01067 Dresden www.dresden-congresscenter.de

The accompanying exhibition is scheduled from 20 to 22 March, 2018, and will take place on the Terrace Level of the ICCD, which also hosts the coffee break area.

## **Interactive Programme Online**

A fully interactive DATE 2018 programme is available on the website **www.date-conference.com** where you will be able to view the entire details of the programme and plan your attendance in advance.

## **Internet Access**

Free wireless internet access is available on-site throughout the whole congress center during the entire DATE week. The WLAN login code will be provided at the registration desk upon arrival (entrance foyer of the congress center).

## **Proceedings**

The conference proceedings are available on USB Stick on-site (sponsored by Texas Instruments) for every fully registered conference delegate.

## WHOVA Conference App

The Whova app can be downloaded via the following link or in the Apple/Google stores for free: https://whova.com/download Please install the app and search for the conference "DATE 2018"

→ Password: "DATE"

A browser version can be accessed at https://whova.com/webapp/e/datec\_201803/

Online Conference Evaluation via the WHOVA App ("survey" button): every fully registered delegate who fills in the online conference evaluation via the app, will receive one of the exclusive DATE collector mugs at the registration desk (when showing the confirmation page).

A browser version can be accessed at https://www.date-conference.com/survey

## Coffee Break in the Exhibition Area

On all conference days (Tuesday to Thursday), coffee and tea will be served during the coffee breaks at the below-mentioned times in the exhibition area (Terrace Level of the ICCD).

## Lunch Break (Großer Saal + Saal 1)

On all conference days (Tuesday to Thursday), a seated lunch (lunch buffet) will be offered in the rooms "Großer Saal" and "Saal 1" (Saal Level of the ICCD) to fully registered conference delegates only. There will be lunch voucher control at the entrance to the lunch break area.

#### Tuesday, March 20, 2018

| Coffee Break | 1030 - 1130 |

|--------------|-------------|

| Lunch Break  | 1300 - 1430 |

| Coffee Break | 1600 - 1700 |

## Wednesday, March 21, 2018

| Coffee Break                                        | 1000 - 1100 |

|-----------------------------------------------------|-------------|

| Lunch Break                                         | 1230 - 1430 |

| Awards Presentation and Keynote Lecture in "Saal 2" | 1345 - 1420 |

| Coffee Break                                        | 1600 – 1700 |

#### Thursday, March 22, 2018

| Coffee Break                | 1000 - 1100 |

|-----------------------------|-------------|

| Lunch Break                 | 1230 - 1400 |

| Keynote Lecture in "Saal 2" | 1320 - 1350 |

| Coffee Break                | 1530 - 1600 |

## Welcome Reception & PhD Forum Monday, March 19, 2018

All registered conference delegates and exhibition visitors are kindly invited to join the DATE 2018 Welcome Reception & subsequent PhD Forum, which will take place on Monday, March 19, 2018, from 1800 - 2100 in "Saal 1" of the ICC Dresden.

The PhD Forum of the DATE Conference is a poster session and a buffet style dinner hosted by the European Design Automation Association (EDAA), the ACM Special Interest Group on Design Automation (SIGDA), and the IEEE Council on Electronic Design Automation (CEDA). The purpose of the PhD Forum is to offer a forum for PhD students to discuss their thesis and research work with people of the design automation and system design community. It represents a good opportunity for students to get exposure on the job market and to receive valuable feedback on their work.

## GENERAL INFORMATION

## **Exhibition Reception**

## Tuesday, March 20, 2018

The Exhibition Reception will take place on Tuesday, March 20, 2018, from 1830 - 1930 in the exhibition area (Terrace Level), where free drinks for all conference delegates and exhibition visitors will be offered. All exhibitors are welcome to also provide drinks and snacks for the attendees.

## DATE Party | Networking Event Wednesday, March 21, 2018

Wednesday, March 21, 2018 The DATE Party traditionally states one of the highlights of the DATE week. As one of the main networking opportunities during the DATE week, it is a perfect occasion to meet friends and colleagues in a relaxed atmosphere while enjoying local amenities. It is scheduled on March 21, 2018, from 1930 to 2300.

## As in 2017, the DATE Party will again feature the awards presentation of the Best Paper Awards and Best IP Award.

This year, it will take place in one of Dresden's most recognized museum locations, the Deutsches Hygiene-Museum Dresden, which attracts over 300,000 international visitors per year. The Deutsches Hygiene-Museum was founded in 1912 and is a unique museum location. Unlike its traditional name, the museum offers nowadays not just hygiene in the medical or colloquial way. Moreover, visitors may explore in the permanent collection "Adventure Human Being" how people shape their environment and affect society as a physical and intellectual being, and how they are influenced by it vice versa. The museum is located close to the city center and will offer a special setting for the DATE Party 2018.

#### → Please kindly note that it is not a seated dinner.

All delegates, exhibitors and their guests are invited to attend the party. Please note that entrance is only possible with a valid party ticket. Each full conference registration includes a ticket for the DATE Party (which needs to be booked during the online registration process though). Additional tickets can be purchased on-site at the registration desk (subject to availability of tickets). Price for extra ticket: 70 € per person.

## How to get there: A bus shuttle from the congress centre to the Hygiene-Museum Dresden will be organized, starting at 1900 from the main entrance of the ICC Dresden.

Afterwards, busses will be at your disposal for getting back to the city centre, at the following times: 2230 and 2300. You will have the choice between a bus that stops at "Postplatz" and a bus that will stop at the Maritim Hotel & International Congress Centre Dresden.

#### **Route description** → www.dhmd.de/en/your-visit/directions

By public transportation: Take the tram line 4 (Direction: Striesen) from the ICC Dresden (Kongresszentrum/ Haus der Presse stop) to the stop Deutsches Hygienemuseum. Check times here: www.dvb.de

By car: Take the A4 motorway, Hellerau exit or Altstadt exit, Direction Zentrum and follow the signage. Street parking is available.

Walking distance: 10 minutes from the tram stop Deutsches Hygiene-Museum 35 minutes from the ICC Dresden

## GENERAL INFORMATION

## **Interactive Presentations**

(sponsored by the Cadence Academic Network)

Interactive presentations allow presenters to interactively discuss novel ideas and work in progress, which may require additional research work and discussion, with other researchers working in the same area. Interested attendees can walk around freely and talk to any author they want in a vivid face-to-face format. IP presentations will also be accompanied by a poster. Each IP will additionally be introduced in a relevant regular session prior to the IP Session in a one-minute presentation.

To give an overview, there will be one central projection displaying a list of all the presentations going on at the same time in the IP area. Interactive Presentation (IP) Sessions will be held in the foyer of the Conference Level in 30-minute time slots on the following days:

#### Tuesday, March 20, 2018

| IP Session 1 | Conference Level, Foyer | 1600 – 1630 |

|--------------|-------------------------|-------------|

|              |                         |             |

## Wednesday, March 21, 2018

| IP Session 2                      | Conference Level, Foyer                           | 1000 - 1030 |

|-----------------------------------|---------------------------------------------------|-------------|

| IP Session 3                      | Conference Level, Foyer                           | 1600 - 1630 |

| Presentation of the Best IP Award | during the DATE Party<br>(Hygiene-Museum Dresden) | 2100 - 2115 |

#### Thursday, March 22, 2018

| IP Session 4 Conference Level, Foyer 1000 – 1030 |

|--------------------------------------------------|

|--------------------------------------------------|

### Thursday, March 22, 2018

| IP Session 5 | Conference Level, Foyer | 1530 - 1600 |

|--------------|-------------------------|-------------|

|--------------|-------------------------|-------------|

## **EXECUTIVE SESSIONS**

Co-Chairs: Giovanni De Micheli, EPFL, CH Marco Casale-Rossi, Synopsys, IT

Innovation runs strong in our industry: artificial intelligence hardware and software have recently achieved superhuman performances [1]; general purpose quantum computers will be available within the next five years [2], and all the p10 automakers have already announced plans toward SAE level 4, and 5 availability before the end of this decade. Sensors, and actuators will be the essential arms, ears, and eyes of all these technologies. This year Executive Track begins with a panel which gathers world experts to discuss the opportunities and the challenges of these emerging technologies, which may change our lives.

Whether for the good or the bad, depends also on the engineering community: new processors architectures are emerging, superconducting electronics and quantum computing shake the foundations of EDA, and autonomous driving pushes performance, power consumption, and reliability envelope beyond any previous limit. The Executive Track continues with a session on the advances required for the design automation of quantum computing devices, followed by a session on the most recent advances in logic synthesis.

## 2.1 Executive Panel: How Electronics May Change Our Lives, and the World

Moderator: Antun Domic, Synopsys, USA

→ See Page 41

## 3.1 Executive Session: Design Automation for Quantum Computing

Chair: Edoardo Charbon, TU Delft, NE & EPFL, CH Co-Chair: Daniel Große, University of Bremen, DE

→ See Page 46

## 4.1 Executive Session: Exact Synthesis and SAT

Chair: Patrick Vuillod, Synopsys, FR Co-Chair: Luca Amarù, Synopsys, US

→ See Page 52

## SPECIAL DAY – WEDNESDAY

## **Future and Emerging Technologies**

Co-Chairs:

**Robert Wille,** Johannes Kepler University Linz, DE **Subhasish Mitra,** Standford University, US

The demands of future applications far exceed the capabilities of today's computing systems. Yet the progress in traditional computing hardware technologies has begun to stall at the exact moment when these exciting applications are demanding large improvements with respect to functionality, performance, and energy efficiency. Besides that, the impressive progress in the development of semiconductors motivated numerous "Moore-than-Moore"-applications.

This special day will explore transformative concepts that will revolutionize future computing systems. It thereby reflects the broad variety of future and emerging technologies -- ranging from microfluidic devices over photonics and quantum computing to nanosystems. All talks are prepared in the spirit to first provide an overview of the respectively considered technology before open challenges and problems for which design automation methods may help are discussed. This way, the special day aims to trigger a more thorough exchange between the different communities.

5.1 Special Day Session on Future and Emerging Technologies: Challenges for the Design of Microfluidic Devices: EDA for your Lab-on-a-Chip

→ See Page 58

5.1 Special Day Session on Future and Emerging Technologies: Transistors for Digital NanoSystems: The Road Ahead

→ See Page 64

7.0 LUNCH TIME KEYNOTE SESSION: From Inverse Design to Implementation of Robust and Efficient Photonics for Computing

→ See Page 68

Special Day Session on Future and Emerging Technologies: Theoretical and practical aspects of verification of quantum computers

→ See Page 68

Special Day Session on Future and Emerging Technologies: NanoSystems: Connecting Devices, Architectures, and Applications

→ See Page 76

## SPECIAL DAY — THURSDAY

## **Designing Autonomous Systems**

Co-Chairs:

**Rolf Ernst,** Institut für Datentechnik und Kommunikationsnetze, DE **Marco Platzner,** University of Paderborn, DE

Autonomous vehicles and robots are prominent examples for a larger trend towards embedded and cyber-physical systems autonomy serving many purposes: function automation, function adaptation, platform adaptation, and handling the dynamics of function integration on large open networks. In autonomous systems, the current separation of design process and operation in the field will be replaced by a life-time process of in-field adaptation. Continuous change and evolution, application interference, environment dynamics and uncertainty have complex effects which must be controlled thereby adhering to safety, availability, and security guarantees where needed. This special day covers the latest trends in autonomous systems and the resulting challenges for design processes and EDA tools.

The first session addresses embedded machine learning, a core technology for autonomous systems, from its impact on safe automated driving to the design of scalable hardware accelerators. The second session outlines the impact of autonomous systems on the industrial design process, including services, vehicle functionality and its design, and the transition from mechanically dominated to software driven processes in industry 4.0. The lunch time keynote gives an insight in the resulting evolution of the automotive industry from a leading OEM perspective thereby emphasizing new safety and verification challenges. The first afternoon session focuses on another important and growing area of autonomous systems, smart vision systems. The last session is dedicated to the design of self-aware autonomous systems and their applications in avionics and automotive systems.

9.1 Special Day Session on Designing Autonomous Systems: Embedded Machine Learning

→ See Page 82

10.1 Special Day Session on Designing

Autonomous Systems: Digitalization in

automotive and industrial systems

→ See Page 88

11.0

LUNCH TIME KEYNOTE SESSION:

Autonomous Driving: Ready to Market?

Which are the Remaining Top Challenges?

→ See Page 92

11.1 Special Day Session on Designing Autonomous Systems: Smart Vision Systems

→ See Page 93

Special Day Session on Designing Autonomous Systems: Self-awareness for Autonomous Systems

→ See Page 100

12.1

## SPECIAL & EU SESSIONS

#### **Special Session Chairs:**

Giovanni De Micheli, EPFL, CH and Marco Casale-Rossi, Synopsys, IT EU Sessions Chair: Paul Pop, Technical University of Denmark, DK

The following Special Sessions have been organized, which should be of great general interest, and make a technical status about topics such as security for Internet-of-Things devices and applications, image recognition, machine learning processors, emerging devices, memories, and architectures:

## 2.7 Special Session: Spintronics based New Computing Paradigms and Applications

Chair: Weisheng Zhao, Beihang University, PRC Co-Chair: Mehdi Tahoori, Karlsruhe Institute of Technology, DE

→ See Page 44

4.6 Special Session: Securing Power-constrained System-on-Chips: Challenges and Opportunities

Chair: Saibal Mukhopadhyay, Georgia Institute of Technology, USA

→ See Page 55

5.4 Special Session: Lightweight Security for Resources-Constrained Internet-of-Things Applications

**Chair: Basel Halak,** University of Southampton, UK **Co-Chair: Yier Jin Jin Yier,** University of Florida, USA

→ See Page 59

6.5 Special Session: Three Years of Low-Power Image Recognition Challenge

Chair: Yung-Hsiang Lu, Purdue University, USA

→ See Page 66

7.6 Special Session: Next Generation Processors and Architectures for Deep Learning

Chair: Theocharis Theocharides, University of Cyprus, CY Co-Chair: Muhammad Shafique, TU Wien, AT

→ See Page 72

8.2

EU Projects: Novel Technologies, Predictable Architectures and Worst-Case Execution Times

Chair: Paul Pop, Technical University of Denmark, DK Co-Chair: Petru Eles, Linköping University, SE

→ See Page 76

9.4 EU Projects: Novel Platforms – from Self-Aware MPSoCs to Server Ecosystems

**Chair: Martin Schoeberl,** Technical University of Denmark, DK **Co-Chair: Flavius Gruian,** Lund University, SE

→ See Page 84

10.6 Special Session: Computing with Ferroelectric FETs - Devices, Models, Systems, and Applications

Organizer: Michael Niemier, Notre Dame University, USA Co-Chair: O'Connor, Ecole Centrale de Lyon, FR

→ See Page 91

12.6 Special Session: Computing with Emerging Memories: How Good can it be?

Organizer: Pierre-Emmanuel Gaillardon, University of Utah, USA Co-Chair: O'Connor, Ecole Centrale de Lyon, FR

→ See Page 103

## **EVENT OVERVIEW**

## NOM No

- 2nd IoT Student Challenge sponsored by IEEE CEDA and Texas Instruments

- Afternoon Tutorials

- EDA Forum: Advancing Diversity in EDA

- Welcome Reception & PhD Forum, hosted by EDAA, ACM SIGDA, and IEEE CEDA

1

- Opening Session: Plenary, Awards Ceremony & Keynote Addresses

- Executive Sessions

- · Technical Conference

- Vendor Exhibition & Exhibition Theatre

- Interactive Presentation IP1

- · University Booth

- Fringe Meetings & Co-Located Workshops

- · Exhibition Reception

- Technical Conference

- · Vendor Exhibition & Exhibition Theatre

- · Special Day on "Future and Emerging Technologies" and Keynote

- Interactive Presentations IP2 and IP3

- · University Booth

- Fringe Meetings & Co-Located Workshops

- · DATE Party | Networking Event

Ξ

WED

- · Technical Conference

- · Vendor Exhibition & Exhibition Theatre

- · Special Day on "Designing Autonomous Systems" and Keynote

- Fringe Meetings & Co-Located Workshops

- Interactive Presentations IP4 and IP5

- · University Booth

Ē,

· Special Interest Workshops

## CONTACTS

#### **DATE 2018 Conference Organization**

c/o K.I.T. Group GmbH Dresden Bautzner Str. 117 – 119 01099 Dresden, Germany Email: date@kitdresden.de

#### **Conference Manager:**

Franziska Röhrig K.I.T. Group GmbH Dresden, DE Phone: +49 351 4967 541

## **Exhibition Manager:**

Kathleen Schäfer K.I.T. Group GmbH Dresden, DE Phone: +49 351 4842 964

#### Registration & Accommodation:

Elisa Antonucci

K.I.T. Group GmbH Dresden, DE Phone: +49 351 4823 733 date-registration@kitdresden.de

| 1330      | Tutorial and Confer                                                                                        | ence Registration                                                                                                                       | ICCD main entrance                                                               | 1                                                                                                    |

|-----------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 1530–1600 | Tutorial Coffee Bre                                                                                        | ak                                                                                                                                      |                                                                                  |                                                                                                      |

|           | Registered particip<br>tutorials during the                                                                |                                                                                                                                         | tutorial and may m                                                               | ove between                                                                                          |

|           | Konferenz 1                                                                                                | Konferenz 2                                                                                                                             | Konferenz 3                                                                      | Konferenz 4                                                                                          |

| 1400—1800 | M01 Design: Emerging Technologies for Computing – From Devices to Systems                                  | M02<br>Applications:<br>Effective System<br>Level Simulation<br>Techniques and<br>Cross-Layer<br>Perspectives<br>on Low Power<br>Design | M03<br>Test:<br>Reliability: From<br>Physics to CAD                              | M04<br>Embedded:<br>Industrial<br>Internet-of-Things:<br>Architectures,<br>Designs and<br>Challenges |

|           | Konferenz 5                                                                                                | Seminar 3+4                                                                                                                             | Seminar 5+6                                                                      |                                                                                                      |

| 1400–1800 | M05<br>Industrial A: How<br>to Implement<br>Domain-Specific<br>Modeling<br>Languages:<br>Hands-on Tutorial | M06 Industrial B: Building Arm Cortex-M Powered Internet of Things (IoT) Applications: From Design to Deployment                        | M07<br>Industrial C:<br>Computer Vision<br>for Automated<br>Driving in<br>MATLAB |                                                                                                      |

| 1800–2100 |                                                                                                            | n & PhD Forum, incl<br>CEDA IoT Student C                                                                                               | . Awards Presentation<br>hallenge Prize) Sa                                      | on (PhD Forum<br>al 1                                                                                |

## MONDAY EVENTS

March 19, 2018, 0900 - 1800, Konferenz 6

FM03

and IoT Student Challenge, sponsored by IEEE CEDA and Texas Instruments

Organiser: Akash Kumar, Technische Universitaet Dresden, DE

FM04

March 19, 2018, 1400 – 1800, Seminar 1 (Attendance free of charge)

Forum: Advancing Diversity in Electronic

Design Automation (DivEDA)

Organisers: Ayse Coskun, Boston University, US

Eli Bozorgzadeh, University of California, Irvine, US

## TUESDAY 20 MARCH, 2018

| 0730        | Registration   Spea                                                                     | ker's Breakfast, Saa                                  | l1                                                            |                                                                           |

|-------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------|

| 0830-1030   | 1.1 Opening Sessio<br>Großer Saal                                                       | n: Plenary, Awards (                                  | Ceremony & Keynote                                            | Addresses                                                                 |

| 1030-1130   |                                                                                         | Exhibition and                                        | l Coffee Break                                                |                                                                           |

|             | Track 1                                                                                 | Track 2                                               | Track 3                                                       | Track 4                                                                   |

|             | Saal 2                                                                                  | Konf. 6                                               | Konf. 1                                                       | Konf. 2                                                                   |

| 1130 – 1300 | 2.1<br>Executive Panel:<br>How Electronics<br>May Change Our<br>Lives, and the<br>World | 2.2<br>Energy Efficient<br>Neural Networks            | 2.3<br>High-Level<br>Synthesis                                | 2.4<br>Model Checking                                                     |

| 1300 – 1430 |                                                                                         | Lunch Break, Gro                                      | ßer Saal + Saal 1                                             |                                                                           |

|             | Saal 2                                                                                  | Konf. 6                                               | Konf. 1                                                       | Konf. 2                                                                   |

| 1430 – 1600 | 3.1<br>Executive<br>Session: Design<br>Automation<br>for Quantum<br>Computing           | 3.2<br>Approximate and<br>Near-Threshold<br>Computing | 3.3<br>Optimization<br>Techniques for<br>MPSoCs               | 3.4 Optimizing Computing with Neuromorphic Architectures and Accelerators |

| 1600 – 1700 | 1600 – 1630                                                                             |                                                       | I Coffee Break<br>entations, Conferenc                        | e Level, Foyer                                                            |

|             | Saal 2                                                                                  | Konf. 6                                               | Konf. 1                                                       | Konf. 2                                                                   |

| 1700 – 1830 | 4.1<br>Executive<br>Session: Exact<br>Synthesis and<br>SAT                              | 4.2<br>Domain<br>Specific Design<br>Methodologies     | 4.3<br>System Modelling<br>for Simulation and<br>Optimisation | 4.4<br>Overcoming the<br>Limitations of<br>Worst-Case IC<br>Design        |

| 1830 – 1930 | EV                                                                                      | HIRITION DECEDTION                                    | N in the Exhibition A                                         | rea                                                                       |

| 1830 - 1930 | EX                                                                                      | HIBITIUN KECEPTIC                                     | IN IN THE EXHIBITION A                                        | rea                                                                       |

Plenary OPENING

Executive Sessions Special &

Special & EU Session

IP Session

**Exhibition Theatre**

## TUESDAY 20 MARCH, 2018

| Registration   Spea                                                  | ker's Breakfast, Saa                                                                                             | 11                                                                                             |                                                                     | 0730        |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------|

| 1.1 Opening Sessio<br>Großer Saal                                    | n: Plenary, Awards (                                                                                             | Ceremony & Keynote                                                                             | Addresses                                                           | 0830-1030   |

|                                                                      | Exhibition and                                                                                                   | l Coffee Break                                                                                 |                                                                     | 1030-1130   |

| Track 5                                                              | Track 6                                                                                                          | Track 7                                                                                        | TRACK 8                                                             |             |

| Konf. 3                                                              | Konf. 4                                                                                                          | Konf. 5                                                                                        | Exhibition Theatre                                                  |             |

| 2.5<br>GPU and<br>GPU-based<br>heterogeneous<br>system<br>management | 2.6<br>Circuit Locking<br>and Camouflaging                                                                       | 2.7<br>Special Session:<br>Spintronics based<br>New Computing<br>Paradigms and<br>Applications | 2.8<br>Enabling ICT<br>Innovations for<br>European SMEs             | 1130 – 1300 |

|                                                                      | Lunch Break, Gro                                                                                                 | ßer Saal + Saal 1                                                                              |                                                                     | 1300 – 1430 |

| Konf. 3                                                              | Konf. 4                                                                                                          | Konf. 5                                                                                        | Exhibition Theatre                                                  |             |

| 3.5<br>Memory<br>Reliability                                         | 3.6<br>Real-time<br>Multiprocessing                                                                              |                                                                                                | 3.8<br>Innovative<br>Products for<br>Autonomous<br>Driving (part 1) | 1430 – 1600 |

| 1600 – 1630                                                          | Exhibition and<br>IP1 Interactive Pres                                                                           | l Coffee Break<br>entations, Conferenc                                                         | ce Level, Foyer                                                     | 1600 – 1700 |

| Konf. 3                                                              | Konf. 4                                                                                                          | Konf. 5                                                                                        | Exhibition Theatre                                                  |             |

| 4.5<br>Test: innovative<br>infrastructures<br>and ATPG<br>techniques | 4.6<br>Special Session:<br>Securing Power-<br>constrained<br>System-on-Chips:<br>Challenges and<br>Opportunities | 4.7<br>Adaptive Reliable<br>Computing Using<br>Memristive and<br>Reconfigurable<br>Hardware    | 4.8<br>Components<br>for Secure IoT<br>Systems                      | 1700 – 1830 |

| EX                                                                   | HIBITION RECEPTIO                                                                                                | N in the Exhibition A                                                                          | rea                                                                 | 1830 – 1930 |

|                                                                      |                                                                                                                  |                                                                                                |                                                                     |             |

T-Track

E-Track

A-Track

D-Track

## WEDNESDAY 21 MARCH, 2018

| 0730                       | Registration   Spea                                                                                                                                                    | ker's Breakfast, Saa                                                           | l 1                                                                    |                                                                                                                           |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|                            | Track 1                                                                                                                                                                | Track 2                                                                        | Track 3                                                                | Track 4                                                                                                                   |

|                            | Saal 2                                                                                                                                                                 | Konf. 6                                                                        | Konf. 1                                                                | Konf. 2                                                                                                                   |

| 0830-1000                  | 5.1 Special Day<br>Session on Future<br>and Emerging<br>Technologies:<br>Challenges for<br>the Design of<br>Microfluidic<br>Devices: EDA<br>for your Lab-on-<br>a-Chip | 5.2<br>Smart Energy<br>and Automotive<br>Systems                               | 5.3<br>Heterogeneous<br>multi-level<br>caching                         | 5.4<br>Special Session:<br>Lightweight<br>Security for<br>Resources-<br>Constrained<br>Internet-of-Things<br>Applications |

| 1000 – 1100                | Exhibition and Coffe<br>1000 – 1030 IP2 Ir                                                                                                                             | ee Break<br>nteractive Presentat                                               | ions Conference L                                                      | evel, Foyer                                                                                                               |

|                            | Saal 2                                                                                                                                                                 | Konf. 6                                                                        | Konf. 1                                                                | Konf. 2                                                                                                                   |

| 1100 – 1230                | 6.1<br>Special Day<br>Session on Future<br>and Emerging<br>Technologies:<br>Transistors for<br>Digital Nano-<br>Systems: The<br>Road Ahead                             | 6.2<br>Memory Security                                                         | 6.3<br>Advances in<br>AMS/RF Design &<br>Test Automation<br>and Beyond | 6.4<br>Modeling, Control<br>and Scheduling<br>for Cyber-<br>Physical Systems                                              |

| 1230 – 1430                |                                                                                                                                                                        | er Saal + Saal 1<br>ards Presentation<br>LUNCH TIME KEYNO                      | TE SESSION Saal                                                        | 2                                                                                                                         |

|                            |                                                                                                                                                                        |                                                                                |                                                                        |                                                                                                                           |

|                            | Saal 2                                                                                                                                                                 | Konf. 6                                                                        | Konf. 1                                                                | Konf. 2                                                                                                                   |

| 1430 – 1600                | 7.1 Special Day Session on Future and Emerging Technologies: Theoretical and practical aspects of verification of quantum computers                                    | Konf. 6 7.2 Run-time power estimation and optimization                         | 7.3<br>Advances in<br>Logic Synthesis<br>and Technology<br>Mapping     | 7.4                                                                                                                       |

|                            | 7.1 Special Day Session on Future and Emerging Technologies: Theoretical and practical aspects of verification of quantum computers  Exhibition and Coff               | 7.2<br>Run-time power<br>estimation and<br>optimization                        | 7.3<br>Advances in<br>Logic Synthesis<br>and Technology<br>Mapping     | 7.4<br>DRAM and NVMs                                                                                                      |

| 1430 – 1600<br>1600 – 1700 | 7.1 Special Day Session on Future and Emerging Technologies: Theoretical and practical aspects of verification of quantum computers  Exhibition and Coff               | 7.2<br>Run-time power<br>estimation and<br>optimization                        | 7.3<br>Advances in<br>Logic Synthesis<br>and Technology<br>Mapping     | 7.4<br>DRAM and NVMs                                                                                                      |

|                            | 7.1 Special Day Session on Future and Emerging Technologies: Theoretical and practical aspects of verification of quantum computers  Exhibition and Coffi              | 7.2 Run-time power estimation and optimization  ee Break eractive Presentation | 7.3 Advances in Logic Synthesis and Technology Mapping                 | 7.4<br>DRAM and NVMs                                                                                                      |

## WEDNESDAY 21 MARCH, 2018

| Registration   Spea                                                                            | ker's Breakfast, Saa                                                                               | 11                                                                                             |                                                                                                                                       | 0730        |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Track 5                                                                                        | Track 6                                                                                            | Track 7                                                                                        | TRACK 8                                                                                                                               |             |

| Konf. 3                                                                                        | Konf. 4                                                                                            | Konf. 5                                                                                        | Exhibition Theatre                                                                                                                    |             |

| 5.5<br>Emerging<br>Technologies for<br>Future Computing                                        | 5.6<br>Reliability<br>improvement<br>and evaluation<br>techniques                                  | 5.7<br>Software-centric<br>techniques<br>for embedded<br>systems                               |                                                                                                                                       | 0830-1000   |

| Exhibition and Coff<br>1000 – 1030 IP2 Ir                                                      | ee Break<br>nteractive Presentat                                                                   | ions Conference L                                                                              | evel, Foyer                                                                                                                           | 1000 – 1100 |

| Konf. 3                                                                                        | Konf. 4                                                                                            | Konf. 5                                                                                        | Exhibition Theatre                                                                                                                    |             |

| 6.5<br>Special<br>Session: Three<br>Years of Low-<br>Power Image<br>Recognition<br>Challenge   |                                                                                                    |                                                                                                | 6.8<br>Innovative<br>Products for<br>Autonomous<br>Driving (part 2)                                                                   | 1100 – 1230 |

|                                                                                                | er Saal + Saal 1<br>ards Presentation<br>LUNCH TIME KEYNO                                          | TE SESSION Saal                                                                                | 2                                                                                                                                     | 1230 – 1430 |

| Konf. 3                                                                                        | Konf. 4                                                                                            | Konf. 5                                                                                        | Exhibition Theatre                                                                                                                    |             |

| 7.5<br>Reliability<br>Modeling and<br>Mitigation                                               | 7.6<br>Special Session:<br>Next Generation<br>Processors and<br>Architectures for<br>Deep Learning | 7.7<br>Rigorous design,<br>analysis, and<br>monitoring of<br>dependable<br>embedded<br>systems | 7.8 22FDX – the superior technology for loT, RF, Automotive and Mobility: Advanced Design Methodologies for Ultra-low Power Solutions | 1430 – 1600 |

| Exhibition and Coffee Break<br>1600–1630 IP3 Interactive Presentations Conference Level, Foyer |                                                                                                    |                                                                                                | 1600 – 1700                                                                                                                           |             |

| Konf. 3                                                                                        | Konf. 4                                                                                            | Konf. 5                                                                                        | Exhibition Theatre                                                                                                                    |             |

| 8.5<br>From NBTI to<br>IoT security:<br>industrial<br>experiences                              | 8.6<br>Designing reliable<br>embedded<br>architectures<br>under uncertainty                        |                                                                                                | 8.8 22FDX – the superior technology for IoT, RF, Automotive and Mobility: Best-in Class RF, 5G and mmWave designs                     | 1700 – 1830 |

| DATE Party   Netwo                                                                             | DATE Party   Networking Event Deutsches Hygiene-Museum (incl. Best Paper Awards & Best IP Award)   |                                                                                                |                                                                                                                                       | 1930 – 2300 |

|                                                                                                |                                                                                                    |                                                                                                |                                                                                                                                       |             |

| D-Track                                                                                        | A-Track                                                                                            | T-Track                                                                                        | E-Track                                                                                                                               |             |

## THURSDAY 22 MARCH, 2018

| Registration   Spea                                                                                                                   | ker's Breakfast, Saa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | l1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |