# ADVANCE PROGRAMME

www.date-conference.com

Design, Automation and Test in Europe March 14-18, 2016,

Dresden, Germany

European Design and Automation Association

Electronic Design Automation

IEEE Council on Electronic Design Automation

European Electronic Chips & Systems design Initiative

ACM Special Interest Group on Design Automation

Russian Academy of Sciences

# TECHNICAL CO-SPONSORS

- IEEE Computer Society test technology technical Council (tttC)

- IEEE Solid-State Circuits Society (SSCS)

- International Federation for Information Processing (IFIP)

# **EVENT SPONSORS**

# COMMERCIAL SPONSORS

| Media Partners                                                                   | 002 |

|----------------------------------------------------------------------------------|-----|

| Welcome                                                                          | 004 |

| General Information                                                              | 010 |

| KEYNOTE SPEAKERS                                                                 |     |

| Luc Van den hove, imec, BE                                                       | 006 |

| Antun Domic, Synopsys, Inc., US                                                  | 007 |

| Patrick Leteinturier, Infineon Technologies AG, DE                               | 008 |

| Walden C. Rhines, Mentor Graphics Corporation, US                                | 009 |

| EXECUTIVE TRACK                                                                  | 013 |

| ervant Zorian, Synopsys, US                                                      |     |

| AUTOMOTIVE SYSTEMS                                                               | 014 |

| Samarjit Chakraborty, TU Munich, DE<br>Wolfgang Ecker, Infineon Technologies, DE |     |

| SECURE SYSTEMS                                                                   | 015 |

| Ingrid Verbauwhede, KU Leuven and UCLA, BE<br>Matthias Schunter, Intel, DE       |     |

| SPECIAL SESSIONS                                                                 | 016 |

| Giovanni De Micheli, EPFL, CH                                                    |     |

| Marco Casale-Rossi, Synopsys, IT                                                 |     |

| DATE 2016 — AT A GLANCE                                                          | 018 |

| A brief overview of the event                                                    |     |

| MONDAY TUTORIALS                                                                 | 027 |

| Ten half-day tutorials                                                           |     |

| OPENING PLENARY & AWARDS                                                         | 040 |

| Free for exhibition visitors                                                     |     |

| TECHNICAL SESSIONS                                                               | 041 |

| full listing of DATE technical programme, special sessions                       |     |

| FRIDAY WORKSHOPS                                                                 | 094 |

| Eight full-day workshops                                                         |     |

| EXHIBITION THEATRE PROGRAMME                                                     | 112 |

| ree for exhibition visitors                                                      |     |

| JNIVERSITY BOOTH                                                                 | 118 |

| FRINGE MEETINGS &                                                                | 123 |

| CO-LOCATED WORKSHOPS                                                             |     |

| EXHIBITION GUIDE                                                                 | 129 |

| Committees                                                                       | 154 |

| Detailed Index                                                                   | 158 |

| lenue Plan                                                                       | COA |

PROGRAMME GLIDE

March 14—18, 2016,

Dresden, Germany

The DATE organisation and sponsors would like to extend their warmest gratitude to all press journalists who give DATE coverage in the editorial pages. Listed below are the media houses and publications who generously agree to media partnership with DATE, and whose publications can be found on-site.

# Chip Design

Chip Design covers all of the technical challenges and implementation options engineers face in the development and manufacture of today's complex integrated circuits. Chip Design is the only media network dedicated to the advanced IC Design market. Visit www.chipdesignmag.com to stay informed about the latest developments in chip modeling, architecture, de-

chipdesignmag.com

# Chip Design Magazine

sign, test and manufacture, from EDA tools to digital and analog hardware issues. The System Level Design and Low Power Engineering Portals offer focused editorial content you won't want to miss. And, be sure to visit www.eecatalog.com for valuable information about all of Extension Media's outstanding technology resources.

# Confidential

EDA is a commercial-free publication providing a guiet place for conversation about the Electronic Design Automation industry and its companion technologies. The coverage does not intend to be comprehensive, but does intend to

# **EDA Confidential**

provide some food for thought. To that end, EDA Confidential includes "Recipes", Freddy Santamaria's "Gourmet Corner", as well as "Voices" of other contributing authors, "Off the Record" op-ed pieces, and "Conference" coverage.

www.avcinena.com

# **EDAC**AFÉ

EDACafe.Com is the #1 EDA web portal. Thousands of IC, FPGA and System designers visit EDACafé. com to learn the latest news and research design tools and services. The sites attract more than 75,000 unique visitors each month and leverages TechJobsCafé.com to **EDACafé**

bring you job opportunities targeted to engineering and design. And daily e-newsletters reach more than 40,000 engineering professionals. For more details visitwww. FDACafe.com and www.Tech.JohsCafe.com.

www.edacafe.com

## MEDIA PARTNERS

# EE Times Connecting the Global

EE Times Europe provides marketing professionals in the electronics industry with integrated online and print marketing services. EE Times Europe's print edition is a monthly magazine that brings news, analysis and product and design information to 70,000 highly

www.eetimes.com

# **EE Times Europe**

qualified subscribers in over 40 European countries. EE Times Europe's web site eetimes.eu welcomes over 110,000 monthly unique visitors. EE Times Europe's electronic newsletters reach over 30,000 daily readers.

# **Elektron**ik

# Elektronik i Norden, an important tool for the Nordic electronic industry. We want Elektronik i Norden to be the most important source of information for the Nordic electronic industry (Sweden,

www.elinor.se

## Elektronik i Norden

Finland, Norway and Denmark). A circulation of 25 800 personally addressed copies proves we are the major electronics paper in this area. We publish news, comments and in-depth technical articles.

# Engineering & Technology is packed with articles on the latest technology covering the areas of communications, control, consumer technology, electronics, IT, manufacturing & power engineering. It is Europe's largest circulation engineering magazine, published monthly & offers a global circulation of over 140,000 copies to more than 100 countries & a high pass-on readership. Each member of the Institution of Engineering & Technology (IET) receives a copy as part of their membership package. Readers include design & development engineers, system designers & integrators, solutions providers & installers, engi-

www.eandtmagazine.com

# **Engineering & Technology** Magazine - Published by The IET

neering distributors, consultants, planners, facilities managers & end-users. With its HQ in London & regional offices in Europe, North America & Asia-Pacific, the Institution of Engineering & Technology provides a global knowledge network to facilitate the exchange of ideas & promote the positive role of technology around the World. The Institution of Electrical Engineers, dating from 1889, became the Institution of Engineering & Technology in 2006. It now organises more than 120 conferences & other events each year whilst providing professional advice & briefings to industry, education & governments.

## WELCOME TO DATE 2016

# Dear Colleague,

We proudly present to you the Advance Programme of **DATE 2016.** DATE combines the world's favorite electronic systems design and test conference with an international exhibition for electronic design, automation and test, from system-level hardware and software implementation right down to integrated circuit design.

WELCOME TO DATE 2016

Out of a total of 829 paper submissions received, a large share (42%) is coming from authors in Europe, 29% of submissions are from Asia, 25% from North America, and 4% from the rest of the world. This clearly demonstrates DATE's international character, its global reach and impact.

For the 19th successive year, DATE has prepared an exciting technical programme. With the help of 327 members of the Technical Program Committee, who carried out more than 3000 reviews (about four per submission), finally 199 papers (24%) were selected for regular presentation and 81 additional ones (10%) for interactive presentation.

The DATE conference will be held at the International Congress Centre Dresden, Germany, from March 14 to 18, 2016.

As in the previous years, the conference will start on Monday, with 10 indepth technical tutorials offered from experts of the industrial and academic worlds on innovative as well as foundational topics related to design solutions, power efficiency, the internet of things, secure systems and testing and diagnosis.

The plenary keynote speakers on Tuesday are Luc Van den hove, President and Chief Executive Officer imec, who will present a talk on "From the happy few to the happy many: towards an intuitive internet of things.", and Antun Domic, Executive Vice President and General Manager, Design Group, Synopsys, to talk about "Design will make everything different". On the same day, the **Executive Track** offers a series of business panels discussing hot topics. Executive speakers from companies leading the design and automation industry will address some of the complexity issues in electronics design and discuss about the advanced technology challenges and opportunities.

The main conference programme from Tuesday to Thursday includes 77 technical sessions organized in parallel tracks from the four areas

**D** – Design Methods and Tools

A - Application Design

T - Test and Robustness

**E** – Embedded Systems Software

and several special sessions on Hot Topics such as 3D ICs, In-Memory Computing, Heterogeneous Computing, New Transistor for Hardware Security, Embedded Tutorials on Analog-/Mixed Signal Verification Methods and on the Dark Silicon Problem as well as two sessions on selected EU Projects. In addition, the exciting programme of DATE 2016 will include a panel on past and future challenges in EDA.

Two Special Days in the programme will focus on areas bringing new challenges to the system design community: Automotive Systems and Secure Systems. Each of the Special Days will have a full programme of keynotes, panels, tutorials and technical presentations by leading experts from academia and industry.

During the Special Day on Wednesday on Automotive Systems, a keynote is given by Patrick Leteinturier, Fellow Automotive Systems, Infineon Technologies to talk about "The Car of the future will reinvent personal mobility". In addition, the Automotive Special Day will feature a number of technical talks covering areas such as advanced driver assistance systems, formal methods for automotive software, and various aspects of in-vehicle

Luca Fanucci

Jürgen Teich

as well as long-range automotive communications. Furthermore, a panel with speakers from Infineon, Bosch, Mentor, Yogitech and ETAS will discuss various EDA solutions for the automotive domain and ways to go forward. On **Thursday**, a **keynote** in the frame of the Special Day on Secure Systems will be given by Walden C. Rhines, Chief Executive Officer and Chairman of the Board of Directors, Mentor Graphics on "Secure silicon: enabler for the internet of things". The Secure Systems day starts with an embedded tutorial focusing on low level software attacks, followed by technical papers addressing HW/SW embedded platform modifications for security, and technical papers discussing novel metrics and methods to support design for security and trust. The industrial relevance is illustrated with a special session addressing security challenges from Smart Grid, Industry4.0 and auto-

Additionally, there are numerous Interactive Presentations which are organized into five IP sessions.

The conference is complemented by an **exhibition** which runs for three days (Tuesday - Thursday), offering a comprehensive overview of commercial design and verification tools including vendor seminars and abundant networking possibilities with fringe meetings. This year, there are dedicated campus booths with focus on major trends shaping the future of microelectronics such as IoT and secure systems, Ultra-Low power technologies (FDSOI), 5G wireless networks, 3D-IC integration and automotive systems. On the campus booths major international industrial players and research institutions will jointly share their vision on those trends. With this setup the exhibition provides a unique networking opportunity and states the perfect venue for industries to meet University Professors to foster University Programme and especially for PhD Students to meet future employees.

On Friday, the last day of the DATE week, 8 full-day workshops cover a large number of hot topics related to the design and test of electronic systems. This year, DATE will present a new edition of the successful workshops targeting the manufacturing and utilization of secure devices, the techniques for model implementation fidelity, and the optical/photonic interconnects for computing systems. Additionally, some brand new workshops will take place on advanced MPSoC architectures and resource-awareness, emerging memory solutions, novel paradigms in heterogeneous computing, and modeling techniques for aging and variability.

We wish you a successful and exciting DATE 2016, fruitful discussions in the accompanying exhibition and a memorable DATE Party on Wednesday evening.

DAVE 2016 General Chair

Luca Fanucci University of Pisa, IT

/wih DATE 2016 Programme Chair Jürgen Teich

Friedrich-Alexander-Universität Erlangen-Nürnberg, DE

March 14-18, 2016,

Luc Van den hove

0915 - 0945 Großer Saal

From the happy few to the happy many - Towards 1.1.1 an intuitive internet of things

Luc Van den hove, President and CEO, imec, BE

The last year every high-tech company was talking about the Internet of Things. The coming decade, we will indeed see a rise in smart connected systems. Machines, buildings, vehicles, personal appliances will all be equipped with more intelligence that will be interconnected. Smart systems will be unobtrusive, ultra-small, cheap, intelligent, and ultra-low power. They will include sensors, actuators, and processing and communication abilities, often in a one-chip wireless solution.

Imec aims at bringing the Internet of Things to the next level. Imec develops the building blocks to create an easy-to-use Internet of Things that surrounds us, that interacts with us as individuals, that learns our habits, our preferences, our health... An Internet of Things that will connect diverse unconnected systems. That will turn the massive amount of measured data in information to make the right decisions, to take the right actions exactly as we need or want. Of course taking into account our privacy preferences.

This Intuitive Internet of Things will help manage the sustainability, complexity and safety of our world. It will increase our comfort and wellbeing. Not only of the happy few. Imec will bring the Intuitive Internet of Things to the happy many.

# TUESDAY OPENING CEREMONY

Antun Domic

0945 - 1015 Großer Saal

## **Design Will Make Everything Different**

Antun Domic, Executive Vice President and General Manager, Design Group, Synopsys, Inc., US

How many different silicon manufacturing process technologies will there be at 10, 7, or 5 nanometers? Probably only three. How many design starts will there be at 10, 7, or 5 nanometers? According to IBS1, in 2025 there will be less than 250 design starts at 10 nanometers and below, about 3% of the total number of design starts that year, and only about five of those design starts, i.e. 2% of the 3% (0.05% of the total) will take place in Europe. But this is not the end! This is not even the beginning of the end. There is a great deal of opportunity beyond the relentless progression of Moore's law. Design innovation can be the enabler, and the differentiator, regardless of the process technology node. Automotive is a great example: according to Bosch<sup>2</sup>, electronics represents 80% of the innovation in cars, and 40% of its cost; the car is a computer - actually, over one hundred computers - on four wheels already, and it will get smarter and smarter, with new layers of services and players just around the corner. Design, and design automation can help increase and accelerate innovation, and at the same time, improve efficiency. The "Internet of Things" is another, potentially greater example: smartness going way beyond the phone. Everything will get smarter: cars, homes, cities, agriculture, farming, factories, etc. Most of the IoT enablement and differentiation will stem from design, and design automation, which include IP, and an increasing amount of software. After performance and power consumption, systems reliability and security have already become critical design considerations at the dawn of a new era, in which design will be critical to make everything better.

- [1] Design Starts by Geographic Region 2010-2025, International Business Strategies, Inc. (IBS), 2015

- [2] "Can EDA Solve the Problems of Electronic Design for the Car of the Future?", Peter van Staa, Robert Bosch, TCCAD 2014 Keynote Address

Patrick Leteinturier

1400 - 1430 Saal 2

# 7.0

## The Car of the Future will reinvent personal mobility

WEDNESDAY KEYNOTE ADDRESS

Patrick Leteinturier, Fellow Automotive Systems, Infineon Technologies AG, DE

The regulations for CO2 and pollutant reduction have pushed the automotive industry for more electrification. The internal combustion engines will continue to power our vehicles for decades but will be assisted by electric traction in various xEV architectures. The race for efficiency, environment friendly, and safety will not end here. Automated and autonomous driving cars are opening a new field of benefits, but also a new field of challenges. The engineers will have to reinvent the EE vehicle architecture for new domain control and fail operational systems. The cars will be connected to other cars and the infrastructure with software update over the air. The new vehicles will be real cyber physical systems. This keynote will explore the potential of electronic technologies to solve the new requirements in sensing, controlling, powering, energizing the car of the future.

## Key items:

- Car Electronic system design & Test

- Car EE Architecture

- Car Electrification

- Connected Car

- Car Safety and Security

- Software update over the air

- Form Advance Driver Assistance System to Autonomous Driving

# THURSDAY KEYNOTE ADDRESS

Walden (Wally) C. Rhines

1330 - 1400 Saal 2

# 11.0

# Secure Silicon: Enabler for the Internet of Things

Walden C. Rhines, Chief Executive Officer and Chairman of the Board of Directors, Mentor Graphics Corporation, US

As electronic system hackers penetrate deeper—from applications to embedded software to OS to silicon—the impact of security threats is growing exponentially. Viruses and malware in the operating system, or application layer, are major concerns, but only affect a portion of users. In contrast, even small malicious modifications or compromised performance in the underlying silicon can devastate system security for all users. Growth of the Internet of Things magnifies the impact of the security problem by orders of magnitude.

Since hardware is the root of trust in an electronic product, EDA companies will be increasingly pressured to solve the silicon security problems for their customers. This requires a new paradigm in silicon design creation and verification. The traditional EDA role is to design and then verify that the silicon does what it is supposed to do. Creating secure silicon, however, requires that verification ensure that the chip does nothing that it is NOT supposed to do.

The industry is at the first stage of Secure Silicon awareness; it's going to become big business as future events unfold. Join Wally Rhines as he examines the growing threats to silicon security and EDA's possible solutions.

March 14—18, 2016,

Dresden, Germany

This printed programme is intended to provide delegates with an easy reference document during their attendance at DATE 2016. Full conference information including all technical programme details, information on awards, conference registration costs, information about accommodation, travel offers and social events is available on the conference website www.date-conference.com

# **Dates and Venue**

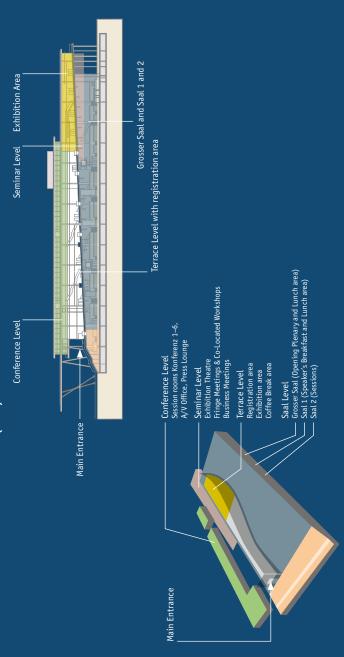

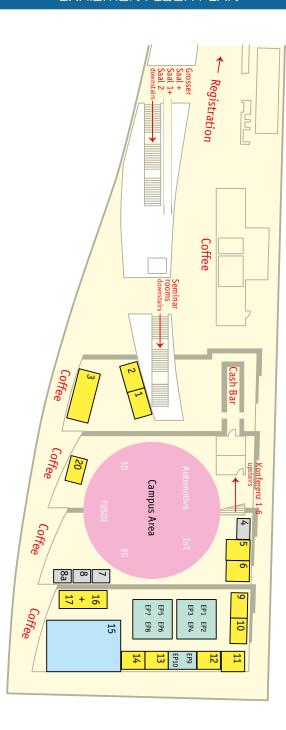

The conference will take place from 14 to 18 March, 2016 in the MARITIM Hotel & International Congress Center Dresden (ICCD).

Maritim Hotel &

International Congress Center Dresden

Ostra-Ufer 2 / Devrientstr. 10 – 12

01067 Dresden, Germany

www.dresden-congresscenter.de

The accompanying exhibition is scheduled from 15 to 17 March, 2016 and will take place on the Terrace Level of the ICCD, which also hosts the coffee break area.

# **Interactive Programme Online**

A fully interactive DATE 2016 programme is available on the web **www.date-conference.com** where you will be able to view the entire details of the programme and plan your attendance in advance.

# **Internet Access**

The conference organisers will again provide free wireless internet access on-site throughout the whole congress center during the entire DATE week. The WLAN login code will be given at the registration desk upon arrival (entrance fover of the congress center).

# **Proceedings**

The conference proceedings are available for download on-site through the DATE-WLAN for every fully registered conference delegate at the following link: www.date-conference.com/proceedings

# WHOVA Conference App

The WHOVA App can be downloaded via the following link or in the Apple/Google stores for free: https://whova.com/download Microsoft users: http://whova.com/webapp/e/date\_201603/

Please install the app and search for the conference "DATE 2016" → Password: "DATE"

Online Conference Evaluation via the WHOVA App ("survey" button): every fully registered delegate who fills in the online conference evaluation via the app, will receive one of the exclusive DATE collector mugs at the registration desk (when showing the confirmation page).

## GENERAL INFORMATION

# **Coffee Break in Exhibition Area**

On all conference days (Tuesday to Thursday), coffee and tea will be served during the coffee breaks at the below-mentioned times in the exhibition area (Terrace Level of the ICCD).

## **Lunch Break**

## Großer Saal + Saal 1

On all conference days (Tuesday to Thursday), a seated lunch (lunch buffet) will be offered in the rooms "Großer Saal" and "Saal 1" (Saal Level of the ICCD) to fully registered conference delegates only. There will be badge control at the entrance to the lunch break area.

## Tuesday, March 15, 2016

| Coffee Break                | 1030 - 1130 |

|-----------------------------|-------------|

| Lunch Break                 | 1300 – 1430 |

| Coffee Break                | 1600 – 1700 |

| Wednesday, March 16, 2016   |             |

| Coffee Break                | 1000 – 1100 |

| Lunch Break                 | 1230 – 1430 |

| Keynote Lecture in "Saal 2" | 1400 – 1430 |

| Coffee Break                | 1600 – 1700 |

| Thursday, March 17, 2016    |             |

| Coffee Break                | 1000 – 1100 |

| Lunch Break                 | 1230 – 1400 |

| Keynote Lecture in "Saal 2" | 1330 – 1400 |

| Coffee Break                | 1530 – 1600 |

|                             |             |

# Welcome Reception & PhD Forum Mon, March 14, 2016

All registered conference delegates and exhibition visitors are kindly invited to join the DATE 2016 Welcome Reception & subsequent PhD Forum, which will take place on Monday, March 14, 2016, from 1800 - 2100 in "Saal 1" of the ICC Dresden.

The PhD Forum of the DATE Conference is a poster session and a buffet style dinner hosted by the European Design Automation Association (EDAA), the ACM Special Interest Group on Design Automation (SIGDA), and the IEEE Council on Electronic Design Automation (CEDA). The purpose of the PhD Fourm is to offer a forum for PhD students to discuss their thesis and research work with people of the design automation and system design community. It represents a good opportunity for students to get exposure on the job market and to receive valuable feedback on their work.

# **Exhibition Reception**

# Tue, March 15, 2016

The Exhibition Reception will take place on Tuesday, March 15, 2016, from 1830 – 1930 in the exhibition area (Terrace Level), where free drinks for all conference delegates and exhibition visitors will be offered. All exhibitors are welcome to also provide drinks and snacks for the attendees.

# GENERAL INFORMATION

# DATE Party – Networking Event Wed, March 16, 2016

The DATE Party traditionally states one of the highlights of the DATE week. As one of the main networking opportunities during the conference, it is a perfect occasion to meet friends and colleagues in a relaxed atmosphere while enjoying local amenities. It is scheduled on March 16, 2016, from 1930 to 2300.

This year, it will take place in one of Dresden's most outstanding museum locations, the Albertinum Dresden.

This museum with its spectacular architecture has been reopened in June 2010 and houses the art gallery "Neue Meister" (New Masters Gallery) and the "Skulpturensammlung" (Sculpture Collection). You may continue the talks and discussions in a relaxed atmosphere while enjoying culinary delights. Furthermore, you will have the possibility to visit parts of the permanent collection.

Please kindly note that it is not a seated dinner.

All delegates, exhibitors and their guests are invited to attend the party. Please be aware that entrance is only possible with a valid party ticket. Each full conference registration includes a ticket for the DATE Party (which needs to be booked during the online registration process though). Additional tickets can be purchased on-site at the registration desk (subject to availability of tickets). Price for extra ticket: 60 € per person.

**How to get there:** A joint walk from the congress centre to the Albertinum Dresden will be organized, starting at 1900 from the main entrance of the ICC Dresden.

# Interactive Presentations (sponsored by the Cadence Academic Network)

Interactive presentations allow presenters to interactively discuss novel ideas and work in progress that may require additional research work and discussion, with other researchers working in the same area. Interested attendees can walk around freely and talk to any author they want in a vivid face-to-face format. The author may illustrate his work with a slide show on a laptop computer, a demonstration, etc. IP presentations will also be accompanied by a poster. Each IP will additionally be introduced in a relevant regular session prior to the IP Session in a one-minute presentation.

To give an overview, there will be one central projection displaying a list of all the presentations going on at the same time in the IP area. Interactive Presentation (IP) Sessions will be held in the foyer of the Conference Level in 30-minute time slots on the following days:

| IP Session 1 | Tuesday, March 15, 2016                          | Conference Level, Foyer           | 1600 – 1630         |

|--------------|--------------------------------------------------|-----------------------------------|---------------------|

| IP Session 2 | Wednesday, March 16, 2016                        | Conference Level, Foyer           | 1000 – 1030         |

| IP Session 3 | Wednesday, March 16, 2016                        | Conference Level, Foyer           | 1600 – 1630         |

|              | Thursday, March 17, 2016<br>of the Best IP Award | Conference Level, Foyer<br>Saal 2 | 1000 – 1030<br>1315 |

| IP Session 5 | Thursday, March 17, 2016                         | Conference Level, Foyer           | 1530 – 1600         |

## EXECUTIVE SESSIONS — TUESDAY

Organiser: Yervant Zorian, Synopsys, US

DATE 2016 will again feature an Executive Track of presentations by leading company executives representing a range of semiconductor manufacturers, EDA vendors, fables houses and IP providers. This one-day programme will be held on Tuesday 15 March, the first day of the DATE conference immediately after the Opening Session and it will be comprised of three sessions where the executives will present their technical/business vision in this nanometer technology era. Each session will feature 3-4 executives and run in parallel to the technical conference tracks.

All three executive sessions will first provide each executive with a timeslot to present his/her vision, followed by a question and answer period to provide interaction with the attendees. The Executive Track should offer prospective attendees valuable information about the vision and roadmaps of their corresponding companies from a business and technology point-of-view for Internet of Things, Automotive and Secure Systems applications.

# 2.1 EXECUTIVE TRACK PANEL:

## **Enabling a Connected World via Internet of Things:**

See Page 41

## 3.1 EXECUTIVE TRACK PANEL:

## **New Opportunities in Automotive Electronics**

See Page 44

# 4.1 EXECUTIVE TRACK PANEL:

## Trends & Challenges to Ensure Security

See Page 50

March 14—18, 2016,

Dresden, Germany

# SPECIAL DAY - WEDNESDAY

Organisers and Chairs: Samarjit Chakraborty, TU Munich, DE Wolfgang Ecker, Infineon Technologies, DE

# **Automotive Systems**

High-end cars today have up to 100 ECUs connected by various communication buses like CAN, FlexRay and Ethernet, that are used to run more than 100 millions of lines of software code spanning across safety critical, driver assistance and comfort related application domains. Designing, verifying and upgrading such a complex hardware/software system poses several challenges for EDA engineers, computer architects, and embedded systems and software designers. Further, most of the innovation in the automotive domain is now in electronics and software, as can be seen in the form of various new driver assistance systems and functionalities. Hence, there are many interesting opportunities for the EDA and the embedded systems community in the automotive domain, which the automotive special day at DATE 2016 will seek to explore in the form of various technical sessions and discussion panels.

5.1 **SPECIAL DAY Hot Topic:**

> **Building Confidence in Advanced Driver Assistance Systems**

See Page 54

**SPECIAL DAY Hot Topic:**

**Formal Methods for Automotive Software**

See Page 59

7.1 SPECIAL DAY Panel:

> Which EDA Solutions can the Automotive Domain Reuse? Very Few or All?

See Page 63

**SPECIAL DAY Hot Topic:**

Connectivity in the automotive domain: From

micro to macro

See Page 69

## SPECIAL DAY - THURSDAY

Organisers and Chairs: Ingrid Verbauwhede, KU Leuven and UCLA, BE

Matthias Schunter, Intel, DE

# **Secure Systems**

Security is essential to create a safe and trustworthy Information and Communications Technology infrastructure. Electronics are becoming more and more integrated into the environment: the Internet of Things, CyberPhysical Systems, Smart Cities are all novel phenomena. Data is stored in and travels from implanted medical devices to the cloud over wireless links and through optical fibers. None of this revolution will be sustainable without adding security. During this special day, several aspects of making systems secure will be addressed. We plan to look at secure HW and SW platforms, address different application domains: automotive, smart grid, or smart factory. We address security versus other functional requirements as dependability and testability, and we investigate design practices for security.

On the first day of the DATE event, half-day in-depth technical tutorials are given by leading experts in their respective fields. The tutorials are well suited for researchers, tool developers and system designers.

SPECIAL DAY Embedded Tutorial:

**Embedded Systems Security**

See Page 74

10.1 **SPECIAL DAY Hot Topic: Lightweight Security for Embedded Processors**

See Page 79

**SPECIAL DAY Hot Topic: Embedded Security Applications**

See Page 83

12.1 **SPECIAL DAY Hot Topic: Design Methods for Security and Trust**

See Page 89

DATE1

Marco Casale-Rossi, Synopsys, IT

The following eight Special Sessions have been organized, which should be of great general interest. Five Hot Topic Sessions make a technical status about emerging topics such as in-memory and embedded computing, hardware security, and 3D-IC. Two embedded tutorials offer an introduction on the latest advances in low power design, and on A&M/S verification. Finally, the Panel Session gathers experts from academia, EDA and semiconductor industry to discuss the challenges of the past and the next decade, what has been solved, and what lies ahead.

2.2

**Embedded Tutorial:**

The Dark Silicon Problem: Technology to the

Rescue?

Organisers: Siddharth Garg, New York University, US

Michael Niemier, University of Notre Dame, US

See Page 41

3.2

**Hot Topic:**

3D ICs: Leap Forward to 1,000X Performance

Organiser: Vikas Chandra, ARM, GB

See Page 45

4.2

**Hot Topic:**

Nanoelectronic Design Tools Addressing Coupled

**Problems for 3D-IC Integration**

Organisers: Jan ter Maten, University of Wuppertal, DE

Caren Tischendorf, Humboldt University of Berlin, DE

See Page 50

5.2

**Hot Topic:**

**In-memory Computing: Status and Trends**

Organiser: Pierre-Emmanuel Gaillardon, University of Utah, US

See Page 54

6.2

Panel:

**Looking Backwards and Forwards**

Organiser: Marco Casale-Rossi, Synopsys, US

See Page 60

## SPECIAL SESSIONS

8.3

**Hot Topic:**

**Managing Heterogeneous Computing**

**Resources at Runtime**

Organisers: Christian Plessl, University of Paderborn, DE

David Andrews, University of Arkansas, US

See Page 70

9.8

**Embedded Tutorial:**

Analog-/Mixed-Signal Verification Methods for

**AMS Coverage Analysis**

Organiser: Gregor Nitsche, OFFIS, DE

See Page 77

12.2

**Hot Topic:**

**Exploiting New Transistor Technologies to Enhance**

Hardware Security (without PUFs!)

Organiser: Michael Niemier, University of Notre Dame, US

See Page 90

## **EUROPEAN PROJECTS**

European Projects Chair: Roberto Giorgi, University of Siena, IT

New this year to DATE is a special session dedicated to European Projects. EU Project Coordinators were invited to submit a paper presenting preliminary ideas, work in progress or lessons learned. The following two special sessions have been formed for presentation based on a peer review that selected the contributions for innovation and originality.

7.2

**EU Projects Special Session: Energy Efficiency** drives Design

Organiser:

Roberto Giorgi, University of Siena, IT

See Page 64

8.2

**EU Projects Special Session: Towards better EU-**

projects - Success Stories

Organiser: Roberto Giorgi, University of Siena, IT

See Page 69

17

## **EVENT OVERVIEW**

## MONDAY

- Educational Tutorials

- Fringe Meetings & Co-Located Workshops

- Welcome Reception & PhD Forum, hosted by EDAA, ACM SIGDA, and IEEE CEDA

## TUESDAY

- Opening Plenary, DATE Awards Ceremony and Keynote Addresses

- Technical Conference

- Vendor Exhibition & Exhibition Theatre

- Executive Sessions

- University Booth

- Fringe Meetings & Co-Located Workshops

- Exhibition Reception

## WEDNESDAY

- Technical Conference

- Vendor Exhibition & Exhibition Theatre

- Special Day on "Automotive Systems" and Keynote

- University Booth

- Fringe Meetings & Co-Located Workshops

- DATE Party Networking Event

# THURSDAY

- Technical Conference

- Vendor Exhibition & Exhibition Theatre

- Special Day on "Secure Systems" and Keynote

- University Booth

- Fringe Meetings & Co-Located Workshops

## FRIDAY

# CONTACTS

## **DATE 2016 Event Secretariat**

c/o K.I.T. Group GmbH Dresden Muenzgasse 2

01067 Dresden, Germany

+49 351 4967 541 Phone:

Fax: +49 351 4956 116 E-Mail: date@kitdresden.de

# **Conference & Exhibition Manager**

Franziska Kremling K.I.T. Group GmbH, DE

+49 351 4967 541 Phone:

## **Registration & Accommodation**

Eva Smejkal

K.I.T. Group GmbH, DE

+49 351 4967 312 Phone:

## MONDAY 14 MARCH

| 0800-<br>0930  | Registration and Tutorial Welcome Refreshments at<br>Conference Level, foyer                                                |                                                                                                                                    |                                                                                                                                         |                                                                                                                                   |                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Breaks         | 1100-1130 Morning Coffee Break<br>1600-1630 Afternoon Coffee Break                                                          |                                                                                                                                    |                                                                                                                                         |                                                                                                                                   |                                                                                                       |

|                | Konferenz 1                                                                                                                 | Konferenz 2                                                                                                                        | Konferenz 3                                                                                                                             | Konferenz 4                                                                                                                       | Konferenz 5                                                                                           |

| 0930-<br>1300  | M01<br>Design<br>solutions:<br>Evolutionary<br>computing<br>in circuit<br>synthesis, op-<br>timization and<br>approximation | M02 Power efficiency: Getting the Current In and the Heat Out — Power Delivery and Thermal Challenges for Mobile Computing Systems | M03<br>Internet-<br>of-Things:<br>Design Meth-<br>odologies and<br>Tools for the<br>Internet-of-<br>Things                              | M04 Secure systems: Design Auto- mation, Test, and Error Recovery: Towards Secure, Dependable, and Adaptive Microfluidic Biochips | M05 Test and diagnosis: Hierarchical Test for Today's SOC and IoT                                     |

| 1300 –<br>1430 | Lunch Prock                                                                                                                 |                                                                                                                                    |                                                                                                                                         |                                                                                                                                   |                                                                                                       |

| 1330           | Conference reg                                                                                                              | gistration begins                                                                                                                  |                                                                                                                                         |                                                                                                                                   |                                                                                                       |

|                | Konferenz 1                                                                                                                 | Konferenz 2                                                                                                                        | Konferenz 3                                                                                                                             | Konferenz 4                                                                                                                       | Konferenz 5                                                                                           |

| 1430 –<br>1800 | M06<br>Design solu-<br>tions: Modern<br>clocking<br>strategies                                                              | M07<br>Power effi-<br>ciency: Power<br>efficiency in<br>the design<br>of Smart IoT<br>devices                                      | M08<br>Internet-of-<br>Things: Virtual<br>Platforms in<br>the Internet-<br>of-Things Era<br>- State of the<br>art and per-<br>spectives | M09<br>Secure<br>systems:<br>Emerging<br>Technologies<br>and Hardware<br>Security:<br>Prospects<br>and Chal-<br>lenges            | M10 Test and diagnosis: Board-level functional fault diagnosis: industry needs and research solutions |

1800 -2100

Welcome Reception & PhD Forum in Saal 1

1830 -

1930

20

#### TUESDAY 15 MARCH TUESDAY 15 MARCH 0730 Registration, Entrance area | Speaker's Breakfast, Saal 1 Registration, Entrance area | Speaker's Breakfast, Saal 1 0730 0830-0830-1.1 Opening Session: Plenary, Awards Ceremony & Keynote Addresses 1.1 Opening Session: Plenary, Awards Ceremony & Keynote Addresses 1030 1030 1030 -1030 -**Exhibition and Coffee Break Exhibition and Coffee Break** 1130 1130 TRACK 1 TRACK 2 TRACK 3 TRACK 4 TRACK 5 TRACK 6 TRACK 7 TRACK 8 Saal 2 Konferenz 6 Konferenz 1 Konferenz 2 Konferenz 3 Konferenz 4 Konferenz 5 **Exhibition Theatre** 1130 -2.2 2.3 2.4 2.5 2.6 2.7 2.8 1130 -1300 **Executive Track** Embedded Automotive Physical Design **Energy Efficient** Fault-Tolerant Variability Revolutionising 1300 for Cutting-edge Panel: Enabling a Tutorial: The Dark Systems and Systems and Embedded Challenges the Teaching Silicon Problem: Connected World Smart Energy Lithography Architectures Systems in Nanoscale of Computer via Internet of Technology to the Systems Designs Architecture and System on Chip Things Rescue? Design 1300 -1300 -Lunch Break Lunch Break 1430 1430 Saal 2 Konferenz 6 Konferenz 1 Konferenz 2 Konferenz 3 Konferenz 4 Konferenz 5 **Exhibition Theatre** 1430 -3.3 3.6 3.7 3.8 1430 -1600 **Executive Track** Hot Topic: **On-Chip Security** Application-Emerging Timing Analysis Dealing with Presentations 1600 3D ICs: Leap Panel: New Testing specific Low-Devices and and Measurement Runtime Failures from FDSOI-Forward to 1,000X Opportunities power Techniques Methodologies for Campus and Energy Efficient from European in Automotive Performance Electronics Systems Projects Booths: Leveraging new Semiconductor Technologies 1600 -1600 -1700 1700 Coffee Break Coffee Break **IP1 Interactive Presentations IP1 Interactive Presentations** Saal 2 Konferenz 6 Konferenz 1 Konferenz 2 Konferenz 3 Konferenz 4 Konferenz 5 **Exhibition Theatre** 1700 -4.3 4.4 4.6 4.8 1700 -Modeling of 1830 **Executive Track** Hot Topic: Firmware Security System-Ultra-low Energy Managing Multi-Presentations 1830 Panel: Trends & Nanoelectronic level Energy Memory Devices Core and Flash Devices and from IoT-Campus Challenges to **Design Tools** Management Memory Mixed-Signal (I): ASIC and Addressing Circuits Sensor Solutions **Ensure Security** Coupled Problems for 3D-IC Integration

D-TRACK

SPECIAL SESSION

A-TRACK

PLENARY SESSION

IP SESSION

T-TRACK

EXECUTIVE SESSION

EXHIBITION THEATRE

E-TRACK

**EXHIBITION RECEPTION**

EXHIBITION RECEPTION

1830 -

1930

| WEDNESDAY | 16  | MARCH |

|-----------|-----|-------|

| ***       | ٠.٠ |       |

| 0730           | Registra                                                                                                       | ation, Entrance area                                                                         | Speaker's Breakfas                                                                  | t, Saal 1                                             |

|----------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------|

|                | TRACK 1                                                                                                        | TRACK 2                                                                                      | TRACK 3                                                                             | TRACK 4                                               |

|                | Saal 2                                                                                                         | Konferenz 6                                                                                  | Konferenz 1                                                                         | Konferenz 2                                           |

| 0830-<br>1000  | 5.1<br>SPECIAL DAY Hot<br>Topic: Building<br>Confidence in<br>Advanced Driver<br>Assistance<br>Systems         | 5.2<br>Hot Topic:<br>In-memory<br>Computing: Status<br>and Trends                            | 5.3<br>Physical<br>Attacks and<br>Countermeasures                                   | 5.4<br>Architectural-<br>level Low-power<br>Design    |

| 1000 —<br>1100 |                                                                                                                |                                                                                              | Break<br>Presentations                                                              |                                                       |

|                | Saal 2                                                                                                         | Konferenz 6                                                                                  | Konferenz 1                                                                         | Konferenz 2                                           |

| 1100 –<br>1230 | 6.1<br>SPECIAL DAY<br>Hot Topic: Formal<br>Methods for<br>Automotive<br>Software                               | 6.2<br>Panel: Looking<br>Backwards and<br>Forwards                                           | 6.3<br>Anti-aging<br>and Error<br>protection using<br>Checkpointing<br>and DVFS     | 6.4<br>Power Modeling<br>and Power Aware<br>Synthesis |

| 1230 –<br>1430 | Lunch Break<br>7.0 SPECIAL DAY Keynote, 1400 – 1430, Saal 2                                                    |                                                                                              |                                                                                     | ıl 2                                                  |

|                | Saal 2                                                                                                         | Konferenz 6                                                                                  | Konferenz 1                                                                         | Konferenz 2                                           |

| 1430 —<br>1600 | 7.1<br>SPECIAL DAY<br>Panel: Which EDA<br>Solutions can<br>the Automotive<br>Domain Reuse?<br>Very Few or All? | 7.2<br>EU Projects<br>Special Session:<br>Energy Efficiency<br>drives Design                 | 7.3<br>Low Power<br>Devices and<br>Methods for<br>Healthcare and<br>Assisted Living | 7.4<br>System-Level<br>Synthesis                      |

| 1600 –<br>1700 |                                                                                                                |                                                                                              | Break<br>Presentations                                                              |                                                       |

|                | Saal 2                                                                                                         | Konferenz 6                                                                                  | Konferenz 1                                                                         | Konferenz 2                                           |

| 1700 –<br>1830 | 8.1<br>SPECIAL DAY<br>Hot Topic:<br>Connectivity in<br>the automotive<br>domain: From<br>micro to macro        | 8.2<br>EU Projects<br>Special Session:<br>Towards better<br>EU-projects -<br>Success Stories | 8.3 Hot Topic: Managing Heterogeneous Computing Resources at Runtime                | 8.4<br>Advanced<br>Methods in High-<br>Level Design   |

| 1930 –<br>2300 | DATE Networking Event (DATE Party)                                                                             |                                                                                              |                                                                                     |                                                       |

|  | 16 MARCH |

|--|----------|

|  |          |

| Registration, Entrance area   Speaker's Breakfast, Saal 1   |                                                                                                                |                                                                                                    |                                                                                                                                             | 0730           |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| TRACK 5                                                     | TRACK 6                                                                                                        | TRACK 7                                                                                            | TRACK 8                                                                                                                                     |                |

| Konferenz 3                                                 | Konferenz 4                                                                                                    | Konferenz 5                                                                                        | Exhibition Theatre                                                                                                                          |                |

| 5.5<br>Alternative<br>Computing<br>Models                   | 5.6<br>Efficient System<br>Modeling with<br>SystemC                                                            | 5.7<br>RF, Power<br>Converters, and<br>ADC: Innovative<br>Design and Test<br>Solutions             | 5.8<br>Model Based<br>Design and<br>Verification Day -<br>Exhibition Keynote<br>and Application<br>Talk                                     | 0830-<br>1000  |

|                                                             |                                                                                                                | Break<br>Presentations                                                                             |                                                                                                                                             | 1000 –<br>1100 |

| Konferenz 3                                                 | Konferenz 4                                                                                                    | Konferenz 5                                                                                        |                                                                                                                                             |                |

| 6.5<br>Biochips                                             | 6.6<br>Modelling and<br>Control of Cyber-<br>Physical Systems                                                  | 6.7<br>Fault tolerant<br>systems and<br>methods                                                    | 6.8<br>Presentations<br>from 5G-Campus<br>and European<br>Projects Booths                                                                   | 1100 –<br>1230 |

| Lunch Break<br>7.0 SPECIAL DAY Keynote, 1400 – 1430, Saal 2 |                                                                                                                |                                                                                                    |                                                                                                                                             | 1230 –<br>1430 |

| Konferenz 3 Konferenz 4 Konferenz 5 Exhibition Theatre      |                                                                                                                |                                                                                                    |                                                                                                                                             |                |

| 7.5<br>Emerging Memory<br>Architectures                     | 7.6<br>Statistical<br>and Symbolic<br>Techniques for<br>the Analysis<br>and Testing<br>of Embedded<br>Software | 7.7<br>Aging mitigation<br>to improve system<br>robustness                                         | 7.8<br>Presentations<br>from IoT-Campus<br>(II): IoT Survival<br>Guide and Big<br>Data Challenges                                           | 1430 –<br>1600 |

| Coffee Break<br>IP3 Interactive Presentations               |                                                                                                                |                                                                                                    |                                                                                                                                             | 1600 –<br>1700 |

| Konferenz 3                                                 | Konferenz 4                                                                                                    | Konferenz 5                                                                                        | Exhibition Theatre                                                                                                                          |                |

| 8.5<br>Non-volatile<br>Memory Design<br>Methodologies       | 8.6<br>Dataflow<br>Modeling and<br>Natural Language<br>Processing                                              | 8.7<br>Test Methods<br>Handling<br>Unkowns, 2.50<br>Integration and<br>Realistic Memory<br>Defects | 8.8<br>Model Based Design and Verification<br>Day - Tutorial: An Industry Approach to<br>FPGA/ARM System<br>Development and<br>Verification | 1700 –<br>1830 |

| DATE Networking Event (DATE Party)                          |                                                                                                                |                                                                                                    |                                                                                                                                             |                |

IP SESSION EXHIBITION THEATRE D-TRACK A-TRACK T-TRACK

E-TRACK

WED

March 14—18, 2016, Dresden, Germany

# THURSDAY 17 MARCH

| 0730           | Registration, Entrance area   Speaker's Breakfast, Saal 1                               |                                                                                                                             |                                                                                       |                                                                       |

|----------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|                | TRACK 1                                                                                 | TRACK 2                                                                                                                     | TRACK 3                                                                               | TRACK 4                                                               |

|                | Saal 2                                                                                  | Konferenz 6                                                                                                                 | Konferenz 1                                                                           | Konferenz 2                                                           |

| 0830-<br>1000  | 9.1<br>SPECIAL DAY<br>Embedded<br>Tutorial:<br>Embedded<br>Systems Security             | 9.2<br>Managing the<br>Traffic Jam in<br>NoC                                                                                | 9.3<br>Industrial<br>Experiences                                                      | 9.4<br>Optimization<br>for Logic and<br>Physical Design               |

| 1000 —<br>1100 |                                                                                         |                                                                                                                             | Break<br>Presentations                                                                |                                                                       |

|                | Saal 2                                                                                  | Konferenz 6                                                                                                                 | Konferenz 1                                                                           | Konferenz 2                                                           |

| 1100 –<br>1230 | 10.1<br>SPECIAL DAY Hot<br>Topic: Lightweight<br>Security for<br>Embedded<br>Processors | 10.2<br>Does it Work or<br>NoC?                                                                                             | 10.3<br>Design<br>Experiences for<br>Multimedia and<br>Communication<br>Applications  | 10.4<br>Stochastic<br>Methods for<br>Circuit Analysis &<br>Synthesis  |

| 1230 –<br>1400 |                                                                                         | Lunch<br>st IP Award Presenta<br>0 SPECIAL DAY Keyr                                                                         |                                                                                       |                                                                       |

|                | Saal 2                                                                                  | Konferenz 6                                                                                                                 | Konferenz 1                                                                           | Konferenz 2                                                           |

| 1400 –<br>1530 | 11.1<br>SPECIAL DAY Hot<br>Topic: Embedded<br>Security<br>Applications                  | 11.2<br>Beating New<br>Technology Paths<br>for NoC                                                                          | 11.3<br>Microarchitec-<br>tures and Work-<br>load Allocation for<br>Energy Efficiency | 11.4<br>Automating Test<br>Generation,<br>Assertions and<br>Diagnosis |

| 1530 —<br>1600 | Coffee Break<br>IP5 Interactive Presentations                                           |                                                                                                                             |                                                                                       |                                                                       |

|                | Saal 2                                                                                  | Konferenz 6                                                                                                                 | Konferenz 1                                                                           | Konferenz 2                                                           |

| 1600 –<br>1730 | 12.1<br>SPECIAL DAY<br>Hot Topic: Design<br>Methods for<br>Security and Trust           | 12.2<br>Hot Topic: Exploit-<br>ing New Transis-<br>tor Technologies<br>to Enhance Hard-<br>ware Security<br>(without PUFs!) | 12.3<br>System Support<br>for Resilience and<br>Robustness                            | 12.4<br>Simulating<br>Everything:<br>From Timing to<br>Instructions   |

|                    | D-TRACK |

|--------------------|---------|

| SPECIAL SESSION    | A-TRACK |

| SPECIAL SESSION    | A-TRACK |

| IP SESSION         | T-TRACK |

| EXHIBITION THEATRE | E-TRACK |

# THURSDAY 17 MARCH

| Registration, Entrance area   Speaker's Breakfast, Saal 1           |                                                                       |                                                            |                                                                                                                  | 0730           |

|---------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------|

| TRACK 5                                                             | TRACK 6                                                               | TRACK 7                                                    | TRACK 8                                                                                                          |                |

| Konferenz 3                                                         | Konferenz 4                                                           | Konferenz 5                                                | Exhibition Theatre                                                                                               |                |

| 9.5<br>Formal Bit Precise<br>Reasoning                              | 9.6<br>Real-Time<br>Scheduling                                        | 9.7<br>Temperature<br>Awareness<br>in Computing<br>Systems | 9.8<br>Embedded<br>Tutorial: Analog-/<br>Mixed-Signal<br>Verification<br>Methods for<br>AMS Coverage<br>Analysis | 0830-<br>1000  |

|                                                                     |                                                                       | Break<br>Presentations                                     |                                                                                                                  | 1000 –<br>1100 |

| Konferenz 3                                                         | Konferenz 4                                                           | Konferenz 5                                                | Exhibition Theatre                                                                                               |                |

| 10.5<br>Enhancing<br>Memory in<br>Next-Generation<br>Platforms      | 10.6<br>Compilers and<br>Tools for GPUs<br>and MPSoCs                 | 10.7<br>Reliable System<br>Design                          | 10.8 Presentations from Campus 3D-IC Integration: Opportunities for SMEs and Outlook 2020+                       | 1100 –<br>1230 |

|                                                                     | Lunch<br>st IP Award Presenta<br>0 SPECIAL DAY Keyi                   |                                                            |                                                                                                                  | 1230 –<br>1400 |

| Konferenz 3                                                         | Konferenz 4                                                           | Konferenz 5                                                | Exhibition Theatre                                                                                               |                |

| 11.5<br>Design of Efficient<br>Microarchitec-<br>tures              | 11.6<br>Applications of<br>Reconfigurable<br>Computing                | 11.7<br>Naked Analog<br>Synthesis                          | 11.8<br>Launch of the<br>Worldwide MEMS<br>Design Contest<br>(Part 1)                                            | 1400 -<br>1530 |

| Coffee Break<br>IP5 Interactive Presentations                       |                                                                       |                                                            |                                                                                                                  |                |

| Konferenz 3                                                         | Konferenz 4                                                           | Konferenz 5                                                | Exhibition Theatre                                                                                               |                |

| 12.5<br>Accelerator<br>Design and<br>Heterogeneous<br>Architectures | 12.6<br>Reconfigurable<br>Computing<br>Platforms and<br>Architectures | 12.7<br>Formal System<br>Level Verification                | 12.8<br>Launch of the<br>Worldwide MEMS<br>Design Contest<br>(Part 2)                                            | 1600 –<br>1730 |

# FRIDAY 18 MARCH

| 0730 –<br>0830 Workshop Registration and Welcome Refreshments                                                      |                                                                                                              |                                                                         |                                                                                                                                   |  |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                    | e individual workshop pi<br>ind break times                                                                  | rogrammes                                                               |                                                                                                                                   |  |

| 0830 – 1700<br>Konferenz 6                                                                                         | 0830 – 1620<br>Konferenz 1                                                                                   | 0830 – 1700<br>Konferenz 5                                              | 0830 – 1500<br>Konferenz 2                                                                                                        |  |

| W01<br>TRUDEVICE<br>2016: Workshop<br>on Trustworthy<br>Manufacturing and<br>Utilization of Secure<br>Devices      | W02<br>3rd Workshop on<br>Design Automation<br>for Understanding<br>Hardware Designs,<br>DUHDe 2016          | W03<br>2nd Workshop<br>on Model-<br>Implementation<br>Fidelity, MiFi'16 | W04 IMPAC: Getting more for less: Innovative MPSoC Architecture Paradigms for Analysability and Composability of Timing and Power |  |

| 0830 – 1700<br>Seminar 5-6                                                                                         | 0830 – 1715<br>Konferenz 3                                                                                   | 0815–1700<br>Konferenz 4                                                | 0830 – 1630<br>Seminar 3-4                                                                                                        |  |

| W05<br>ERMAVSS:<br>Workshop on Early<br>Reliability Modeling<br>for Aging and<br>Variability in Silicon<br>Systems | W06 The 2nd International Workshop on Optical/Photonic Interconnects for Computing Systems (OPTICS Workshop) | W07<br>International<br>Workshop on<br>Emerging Memory<br>Solutions     | W08 First Workshop on Resource Awareness and Application Autotuning in Adaptive and Heterogeneous Computing                       |  |

DATE 16

| 0800 - 0930     | REGISTRATION AND TUTORIAL WELCOME REFRESHMENTS                                                                                       |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0930 - 1300     | TUTORIALS (1100-1130 Coffee Break)                                                                                                   |

| M□1 Konferenz 1 | DESIGN SOLUTIONS: EVOLUTIONARY COMPUTING IN CIRCUIT SYNTHESIS, OPTIMIZATION AND APPROXIMATION                                        |

| MO2 Konferenz 2 | POWER EFFICIENCY: GETTING THE CURRENT IN AND THE HEAT OUT - POWER DELIVERY AND THERMAL CHALLENGES FOR MOBILE COMPUTING SYSTEMS       |

| MO3 Konferenz 3 | INTERNET-OF-THINGS: DESIGN METHODOLOGIES AND TOOLS FOR THE INTERNET-OF-THINGS                                                        |

| M□4 Konferenz 4 | SECURE SYSTEMS: DESIGN AUTOMATION, TEST,<br>AND ERROR RECOVERY: TOWARDS SECURE,<br>DEPENDABLE, AND ADAPTIVE MICROFLUIDIC<br>BIOCHIPS |

| MO5 Konferenz 5 | TEST AND DIAGNOSIS: HIERARCHICAL TEST FOR TODAY'S SOC AND IOT                                                                        |

| 1300 - 1430     | LUNCH BREAK                                                                                                                          |

| 1330            | CONFERENCE REGISTRATION BEGINS                                                                                                       |

| 1430 - 1800     | TUTORIALS (1600-1630 Coffee Break)                                                                                                   |

| MO6 Konferenz 1 | DESIGN SOLUTIONS: MODERN CLOCKING STRATEGIES                                                                                         |

| MO7 Konferenz 2 | POWER EFFICIENCY: POWER EFFICIENCY IN THE DESIGN OF SMART IOT DEVICES                                                                |

| MO8 Konferenz 3 | INTERNET-OF-THINGS: VIRTUAL PLATFORMS IN THE INTERNET-OF-THINGS ERA – STATE OF THE ART AND PERSPECTIVES                              |

| MO9 Konferenz 4 | SECURE SYSTEMS: EMERGING TECHNOLOGIES AND HARDWARE SECURITY: PROSPECTS AND CHALLENGES                                                |

| M10 Konferenz 5 | TEST AND DIAGNOSIS: BOARD-LEVEL FUNCTIONAL FAULT DIAGNOSIS: INDUSTRY NEEDS AND RESEARCH SOLUTIONS                                    |

| 1800 - 2100     | WELCOME RECEPTION & PHD FORUM                                                                                                        |

March 14-18, 2016,

Dresden, Germany

## **TUTORIALS**

# M01

# Design solutions: Evolutionary computing in circuit synthesis, optimization and approximation

Konferenz 1 0930 - 1300

Organisers

Lukas Sekanina, Brno University of Technology, CZ Andy M. Tyrrell, University of York, GB

Genetic and evolutionary algorithms are used in the circuit design and test community mainly as efficient optimization algorithms. Recent years have witnessed a significant development and progress in evolutionary circuit design which is now capable of delivering efficient circuit designs in terms of a multi-objective design scenario, where circuits displaying the best tradeoff among key parameters are automatically sought. The goal of this tutorial is to acquaint the DATE community with the state-of-the-art evolutionary circuit design methods and demonstrate on several case studies how conventional designs can be improved by means of the evolutionary approach.

In the first part of the tutorial, we will briefly introduce the principles of evolutionary computing, evolvable hardware, and multi-objective evolutionary design. We will primarily focus on Genetic Algorithms (GA) and Cartesian Genetic Programming (CGP), as digital circuit design and optimization methods, which will be utilized in the rest of the tutorial. The first case study deals with an efficient multi-objective approach to cell libraries optimization for speed, power, yield and intrinsic variability. A second case study will consider a novel ASIC device specifically designed and fabricated to allow evolution of digital and analogue characteristics and to alleviate the post fabrication variability challenges.

The second half of the tutorial will cover gate-level circuit design, optimization and approximation. CGP will be extended to support functional equivalence checking (based on SAT solving or BDDs) in order to optimize real-world circuits, which was impossible using evolutionary algorithms in the past because of the so-called scalability problems of evolutionary design. Circuit approximation has been developed in recent years as a promising method for constructing energy efficient circuits in some application domains. We will formulate the approximate circuit design problem as a multi-objective design problem and demonstrate its solution for several key circuits (e.g. adders, multipliers, general logic, median) using CGP. Finally we will discuss hardware implementations of evolvable systems in FPGAs and compare approaches based on virtual reconfigurable circuits and dynamic partial reconfiguration.

## □93□ TRANSISTOR-LEVEL EVOLUTION

Chair: Lukas Sekanina, Brno University of Technology, CZ

□93□ Evolutionary computing and evolvable hardware

Andy M. Tyrrell, University of York, GB

1000 Evolutionary approaches to the design of variability-aware cells

Andy M. Tyrrell, University of York, GB