### ADVANCE PROGRAMME

www.date-conference.com

Design, Automation and Test in Europe

March 9

2015

Grenoble,

#### DATE 2015 SPONSORS

European Design and Automation Association

Electronic Design Automation Consortium

IEEE Council on Electronic Design Automation

European Electronic Chips & Systems design Initiative

ACM Special Interest Group on Design Automation

Russian Academy of Sciences

### TECHNICAL CO-SPONSORS

- IEEE Computer Society test technology technical Council (tttC)

- IEEE Solid-State Circuits Society (SSCS)

- International Federation for Information Processing (IFIP)

#### **EVENT SPONSORS**

#### COMMERCIAL SPONSORS

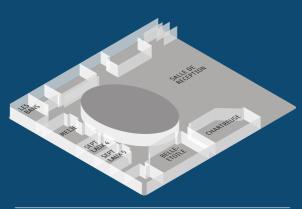

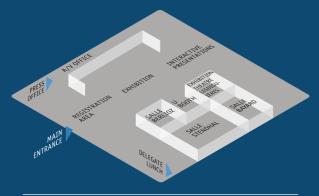

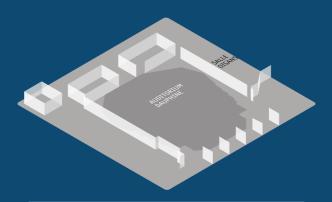

Venue Plan

#### PROGRAMME GUIDE Media Partners 002 Welcome 004 General Information 010 KEYNOTE SPEAKERS Geneviève Fioraso, secrétaire d'Etat chargée de l'Enseignement supérieur et de la Recherche (to be confirmed), FR 006 Günther H. Oettinger, European Commissioner for Digital Economy and Society, DE 006 Jean Marc Chery, Chief Operating Officer of STMicroelectronics, FR 006 Wolfgang Wahlster, German Research Center for Artificial Intelligence, DE 007 Antun Domic, Synopsys, US 008 Kristoffer Famm, GlaxoSmithKline, GB 009 EXECUTIVE TRACK 013Yervant Zorian, Synopsys, US DESIGNING ELECTRONICS FOR THE INTERNET OF THINGS 014 Rolf Drechsler, University of Bremen/DFKI, DE DESIGNING ELECTRONICS FOR MEDICAL APPLICATIONS 015 Jo De Boeck, IMEC, BE SPECIAL SESSIONS 016 Marco Platzner, University of Paderborn, DE Marco Casale-Rossi, Synopsys, IT DATE 2015 - AT A GLANCE 018 A brief overview of the event MONDAY TUTORIALS 027 Ten half-day tutorials OPENING PLENARY & AWARDS 040 Free for exhibition visitors TECHNICAL SESSIONS 041Full listing of DATE technical programme, special sessions FRIDAY WORKSHOPS 097 Ten full-day workshops EXHIBITION THEATRE PROGRAMME 125 Free for exhibition visitors UNIVERSITY BOOTH 129 **EXHIBITION GUIDE** 135 Committees 146 **Detailed Index**

150

C04

2015

Grenoble, France

#### MEDIA PARTNERS

The DATE organisation and sponsors would like to extend their warmest gratitude to all press journalists who give DATE coverage in the editorial pages. Listed below are the media houses and publications who generously agree to media partnership with DATE, and whose publications can be found on-site.

### 3DInCites

#### **3D InCites**

3D InCites is the only online community resource devoted exclusively to the development of interposer and 3D integration technologies including 3D TSVs, 3D ICs and 3D system architectures. Through original contributed content from industry experts, 3D InCites brings to life, the people, the personalities, the ideas, and the minds behind 3D integration.

http://www.3DinCites.com

### Chip Design

Chip Design covers all of the technical challenges and implementation options engineers face in the development and manufacture of today's complex integrated circuits. Chip Design is the only media network dedicated to the advanced IC Design market. Visit www.chipdesignmag.com to stay informed about the latest developments in chip modeling, architecture, design, test

### Chip Design Magazine

and manufacture, from EDA tools to digital and analog hardware issues. The System Level Design and Low Power Engineering Portals offer focused editorial content you won't want to miss. And, be sure to visit www.eecatalog.com for valuable information about all of Extension Media's outstanding technology resources.

http://chipdesignmag.com

#### Confidential

EDA is a commercial-free publication providing a quiet place for conversation about the Electronic Design Automation industry and its companion technologies. The coverage does not intend to be comprehensive, but does intend to provide some food for thought. To that end, EDA Confidential in-

#### **EDA Confidential**

cludes "Recipes", Freddy Santamaria's "Gourmet Corner", as well as "Voices" of other contributing authors, "Off the Record" op-ed pieces, and "Conference" cover-

http://www.aycinena.com

### **EDAC**AFÉ

Thousands of IC, FPGA and System designers visit EDACafé.com to learn the latest news and research design tools and services. The sites attract more than 75,000 unique visitors each month and leverages TechJobsCafé.com to bring you job opportunities targeted to engineering and design. And daily e-newsletters reach more than 30,000

#### **EDACafé**

engineering professionals. EDACafe.com will be doing Executive Video interviews of exhibitors and show organizers at its stand in the Rhodes Hall. For more details visit www.EDACafe.com and www.TechJobsCafe.

http://www.edacafe.com

### **EETimes**

EE Times Europe provides marketing professionals in the electronics industry with integrated online and print marketing services. EE Times Europe's print edition is a monthly magazine that brings news, analysis and product and design information to 70,000 highly qualified subscribers in over

#### **EE Times Europe**

40 European countries. EE Times Europe's web site eetimes.eu welcomes over 110,000 monthly unique visitors. EE Times Europe's electronic newsletters reach over 30,000 daily readers.

http://www.electronics-eetimes.com

#### MEDIA PARTNERS

### ELECTRONIQUE

ElectroniqueS the reference monthly for decision makers and engineers in the electronics sector Circulation of 10,000 copies www. electroniques.biz, the electronic professional's web site Daily Newsletter, the day's essential news about our industry's major sectors Sent to more than 26,000 free sub-

#### **ElectroniqueS**

scribers Weekly newsletter, the newsletter that summarizes the previous 5 daily newsletters main topic Sent to more than 23,000 free subscribers Vertical newsletter, 3 subjects: Automotive / Mil-Aero / Medical 5 mailings a year (each 2 in 3 months)

http://www.electroniques.biz

### Elektronik

Elektronik i Norden, an important tool for the Nordic electronic industry. We want Elektronik i Norden to be the most important source of information for the Nordic electronic industry (Sweden, Finland, Norway and Denmark). A

#### Elektronik i Norden

circulation of 25 800 personally addressed copies proves we are the major electronics paper in this area. We publish news, comments and in-depth technical articles.

http://www.elinor.se

Engineering & Technology is packed with articles on the latest technology covering the areas of communications, control, consumer technology, electronics, IT, manufacturing & power engineering. It is Europe's largest circulation engineering magazine, published monthly & offers a global circulation of over 140,000 copies to more than 100 countries & a high pass-on readership. Each member of the Institution of Engineering & Technology (IET) receives a copy as part of their membership package. Readers include design & development engineers, system designers & integrators, solutions providers & installers, engineering distributors, consultants, planners, facilities man-

### **Engineering & Technology** Magazine - Published by The IET

agers & end-users

With its HQ in London & regional offices in Europe, North America & Asia-Pacific, the Institution of Engineering & Technology provides a global knowledge network to facilitate the exchange of ideas & promote the positive role of technology around the World. The Institution of Electrical Engineers, dating from 1889, became the Institution of Engineering & Technology in 2006. It now organises more than 120 conferences & other events each year whilst providing professional advice & briefings to industry, education & governments.

http://eandt.theiet.org

JB Systems Media is a high tech engineering and media company. JB Systems main areas of interest are among others IoT Embedded Systems, IP Systems,

### **JB Systems Media**

On-Line Education, Systems Engineering & Science.

http://www.jbsystech.com

### EMBARQUÉ

L'Embarqué is a 100% digital media focused on the embedded software and embedded systems market. The media combines a French language web site, several newsletters and a French digital magazine in rich PDF format. The web site www.lembarque. com features a daily updated news feed, various « quest » blogs run by embedded experts and/or VIPs, online job postings and regularly refreshed information on new products. With more than 50 pages displayed in rich PDF format and readable on PCs and tablets, the quarterly digital maga-

#### L'Embarqué

3

zine features interviews, analysis articles written by L'Embarqué journalists, and indepth contributed articles on new embedded hardware or software technologies. Various market fields are addressed by L'Embarqué (mil/aero, medical, industrial, automotive, consumer electronics, telecoms/datacoms...) and the media has a very strong focus on topics related to IoT technologies, software, tools, IP, EDA tools, services and markets.

http://www.lembargue.com

2015,

#### WELCOME TO DATE 2015

#### Dear Colleague,

We proudly present to you the Advance Programme of DATE 2015. DATE combines the world's favorite electronic systems design and test conference with an international exhibition for electronic design, automation and test, ranging from advances on system-level hardware and software implementation to integrated circuit design and nano-technology manufacturing technologies.

DATE 2015 received eligible 915 paper submissions - an all-time high for DATE and a 3% increase over DATE 2014. Besides the large share (45%) of submissions coming from Europe, 24% of submissions are from North-America, 28% from Asia, and 3% from the rest of the world. This proves DATE's international character, its global reach and world-wide impact.

For the 18th successive year, DATE has prepared an exciting technical programme. With the help of the 309 members from its Technical Programme Committee who carried out 3675 reviews (more than four per submission), finally 206 papers (22%) were selected for regular presentation and 86 additional ones (9%) for interactive presentation this year. The DATE 2015 conference will be held at the Alpexpo Congress Center in Grenoble, France, offering once again a truly interesting programme lasting the whole week of March 9 to 13, 2015. On Monday, the conference starts with ten in-depth tutorials. From Tuesday to Thursday, the main technical programme composed of 78 technical sessions comes about. This programme is divided in parallel tracks from four main areas: D - Design Methods and Tools, A - Application Design, T - Test and Robustness; and E - Embedded Systems Software. Finally, on Friday, ten parallel workshops will highlight latest research on hot topics in electronic systems design, such as, 3D design automation, neurocomputing and optical interconnect systems.

This year two of the plenary keynote speakers on Tuesday are EU Commissioner Günther H. Oettinger to talk about European Microelectronics Strategy and Jean Marc Chery, Chief Operating Officer of STMicroelectronics. On the same day, the **Executive Track** offers a series of business panels discussing hot topics. Executive speakers from companies leading the design and automation industry will address some of the complexity issues in electronics design and discuss about the advanced technology challenges and opportunities.

In addition, the distinctive highlights of DATE 2015 are the two special days: "Designing Electronics for the Internet of Things (IoT)" on Wednesday, and "Designing Electronics for Medical Applications" on Thursday. A comprehensive overview regarding both themes will be given, ranging from innovations and applications of latest technologies to analysis of upcoming electronic design automation (EDA) research challenges.

On one hand, the IoT, also known as the "Internet of Anything" promises to realize the omnipresent network of tens of billions of communicating devices. These devices will enable new business models and revolutionize industrial production, logistics and social life, but they will also require dedicated hardware, ultra-low power robust devices and new design methodologies. These topics will be covered by the three keynotes on Wednesday. First, Wolfgang Wahlster (German Research Center for Artificial Intelligence, DE) will address "Industrie 4.0: From the Internet of Things to Cyber-Physical Production Systems". Then, Antun Domic (Synopsys, US) will analyze "The Rise of IoT, and the Role of EDA". Finally,

#### WELCOME TO DATE 2015

Wolfgang Nebel

David Atienza

Hannes Schwaderer (Intel, DE) will highlight the market driven challenges of IoT devices.

On the other hand, providing universal and costly-effective healthcare to the complete human kind has become a major challenge in our modern society. Thus, Thursday will feature an outstanding set of four special sessions on the topic of "Game-changing innovation in health care". This day includes ten trend-setting invited papers, eight of which come from key industrial players in the health care field. Furthermore, one keynote in the frame of the Special Day on Medical Electronics will be given by Kristoffer Famm from GlaxoSmithKline (GSK) to talk about "Bioelectronic Medicines - Heralding in a New Therapeutic Approach".

In addition, numerous Interactive Presentations are organized into five IP sessions during the conference. The accompanying **exhibition** offers a comprehensive overview of commercial design and verification tools including vendor seminars and industrial presentations in the Exhibition Theatre. Moreover, abundant networking possibilities exist with fringe meetings and demonstrations of university research in European projects.

We wish you a successful and exciting DATE 2015 and an entertaining DATE networking event on Wednesday evening, which will take place in the memorable "Musée de Grenoble".

DATE 2015 General Chair Wolfgang Nebel OFFIS & University of Oldenburg, DE

DATE 2015 Programme Chair **David Atienza** EPFL, CH

2015,

Grenoble, France

0830 - 1030 Auditorium Dauphine

1.1.3 **Keynote Address**

Geneviève Fioraso, secrétaire d'Etat chargée de l'Enseignement supérieur et de la Recherche (to be confirmed), FR

Geneviève Fioraso

1.1.4

#### **Keynote Address** Günther H. Oettinger,

European Commissioner for Digital Economy and Society, DE

Günther H. Oettinger

1.1.5

ST technologies fully addressing **Internet of Things** applications from LP Digital to RF-CMOS, eNVM and sensors

Jean Marc Chery, STMicroelectronics, FR

Jean Marc Chery

#### WEDNESDAY KEYNOTE ADDRESS

7.0.1

1250 - 1320Salle Oisans

Industrie 4.0: From the Internet of Things to Cyber-Physical Production **Systems**

> Wolfgang Wahlster, German Research Center for Artificial Intelligence, DE

Wolfgang Wahlster

The Internet of Things is finding its way into production. Semantic machine-to-machine communication revolutionizes factories by decentralized control. Embedded digital product memories guide the flexible work piece flow through smart factories, so that low-volume, high-mix production is realized in a cost-efficient way. A new generation of industrial assistant systems using augmented reality and multimodal interaction will help factory workers to deal with the complexity of cyber-physical production. INDUSTRIE 4.0 is the German strategic initiative to take up a pioneering role in industrial IT that is currently revolutionizing the manufacturing engineering sector. Semantic product memories will play a key role in the upcoming fourth industrial revolution based on cyber-physical production systems. Low-cost and compact digital storage, sensors and radio modules make it possible to embed a digital memory into a product for recording all relevant events throughout the entire lifecycle of the artifact. By capturing and interpreting ambient conditions and user actions, such computationally enhanced products have a data shadow and are able to perceive and control their environment, to analyze their observations and to communicate with other smart objects and human users about their lifelog data. Cyber-physical systems and the Internet of Things lead to a disruptive change in the production architecture: the workpiece navigates through a highly instrumented smart factory and tries to find the production services that it needs in order to meet its individual product specifications stored on the product memory. We illustrate this revolutionary production architecture with examples from DFKI' Smart Factory.

2015,

Grenoble, France

#### WEDNESDAY KEYNOTE ADDRESS

1320 — 1350 Salle Oisans

7.0.2 The rise of IOT, and the role of EDA

Antun Domic, Synopsys, US

Antun Domic

On April 19th, 2015, we will celebrate the 50th anniversary of Moore's law. Process technology went from several microns to a few nanometers, transistors integration capabilities increased millions of times, and volume production grew from the few thousands of units in the early digital computer era to the several billions in the smartphone one. IoT is expected to bring volume production up by one, and perhaps even two orders of magnitude in the next decade. Today, IC volume growth has been anchored on smart phones. Smart everything (cars, homes, cities) may be the next killer application, which would fuel the volume growth. IoT devices and systems will certainly span the entire spectrum, from extremely advanced and complex to "disposable". They will make metrics such as reliability and resilience, be as important as performance, power, and area. But in order for IoT to happen, our industry should dramatically improve its efficiency - all "resources" are scarce, and therefore precious. Flexibility - systems are heterogeneous by nature - and productivity - to deliver the best possible quality-of-results within the allotted turn-around-time - will be critical. As both process technology and system complexity increase, advanced EDA will be a key enabler. Advanced design implementation infrastructure, tools, flows, and methodologies will deliver a competitive advantage, and advanced IP sub-systems, consisting of hardware and software solutions will deliver complete, complex functions, ready for integration, greatly simplifying the IoT "siliconization". These two components show the only viable path towards the trillion units many industry leaders are envisioning.

#### THURSDAY KEYNOTE ADDRESS

1320 — 1350 Salle Oisans

Bioelectronic

Medicines –

Heralding in a

New Therapeutic

Approach

Kristoffer Famm,

GlaxoSmithKline, GB

Kristoffer Famm

Imagine a day when electrical impulses are a mainstay of medical treatment, a day when your doctor will routinely administer microscopic devices that modulate signals in specific nerves for treatment effect. Every organ in our bodies is wired and controlled by nerves, so bioelectronic medicines may be applicable across a broad range of diseases just like molecular medicines are today. Through bioelectronic medicines, GSK, a leading pharmaceutical company, and its extensive network of research collaborators aim to bring the precision and intelligence of electronics right to the core of future treatments.

2015

Grenoble, France

#### GENERAL INFORMATION

This printed programme is intended to provide delegates with an easy reference document during their attendance at DATE 2015. Full conference information including all technical programme details, information on awards, conference registration costs, information about accommodation, travel offers and social events is available on the conference website www.date-conference.com

#### **Dates and Venue**

The conference will take place from 9 to 13 March, 2015, in the Alpexpo Congress Centre

ALPEXPO-ALPES Congres Parc Événementiel de Grenoble Avenue d'Innsbruck – CS 52408 38034 Grenoble cedex 2 France

#### www.alpexpo.com

The accompanying exhibition is scheduled from 10 to 12 March, 2015 and will take place in the foyer of the Alpexpo congress centre, directly next to the session rooms. The spacious area also hosts the poster presentation area as well as coffee break area.

### **Interactive Programme Online**

A fully interactive DATE 2015 programme is available on the web **www.date-conference.com** where you will be able to view the entire details of the programme and plan your attendance in advance.

#### **Internet Access**

There will be free wireless internet access throughout the whole congress center. The WLAN login code will be available on-site at the registration desk (entrance foyer).

#### **WHOVA APP**

The DATE organizers are happy to announce that there will be an app available for the first time at the DATE conference. The WHOVA App can be downloaded via the following link or in the Apple/Google stores for free: https://whova.com/download

Please install the app and search for the conference "DATE 2015" → Password: "DATE"

Online Conference Evaluation via the App ("survey" button): every fully registered delegate who fills in the online conference evaluation via the WHOVA App, will receive a DATE muq at the registration desk (when showing the confirmation page).

### **Proceedings**

The conference proceedings are available for download on-site through the DATE-WLAN for every fully registered conference delegate at the following link: www.date-conference.com/proceedings

#### GENERAL INFORMATION

### **Coffee Break in Exhibition Area**

On all conference days (Tuesday to Thursday), coffee and tea will be served during the coffee breaks at the below-mentioned times in the exhibition area.

#### **Lunch Break**

On Tuesday and Wednesday, lunch boxes will be served in front of the session room Salle Oisans and in the exhibition area for fully registered delegates (a voucher will be given upon registration on-site). On Thursday, lunch will be served in Room Les Ecrins (for fully registered conference delegates only).

#### Tuesday, March 10, 2015

| Coffee Break                                                               | 1030 – 1130                |

|----------------------------------------------------------------------------|----------------------------|

| Lunch Break<br>Keynote session sponsored by Mentor Graphics in room Oisans | 1300 - 1430<br>1320 - 1420 |

| Coffee Break                                                               | 1600 – 1700                |

#### Wednesday, March 11, 2015

| Coffee Break                    | 1000 – 1100 |

|---------------------------------|-------------|

| Lunch Break                     | 1230 – 1430 |

| Keynote lectures in room Oisans | 1250 – 1420 |

| Coffee Break                    | 1600 – 1700 |

#### Thursday, March 12, 2015

| Coffee Break                   | 1000 – 1100 |

|--------------------------------|-------------|

| Lunch Break                    | 1230 - 1400 |

| Keynote lecture in room Oisans | 1320 – 1350 |

| Coffee Break                   | 1530 – 1600 |

#### **Welcome Reception**

#### Mon, March 9, 2015

The organizers kindly invited all registered conference delegates to the DATE 2015 Welcome Reception which will take place on Monday, March 9, 2015, from 1800 - 1900 in the area "Salle de Reception" of the congress center. Subsequently, the PhD Forum will take place from 1900 - 2100 in the same location, where every interested delegate can attend as well.

### **Exhibition Reception**

### Tue, March 10, 2015

The Exhibition Reception will take place on Tuesday, March 10, 2015, from 1830 – 1930 in the exhibition area of the congress center, where free drinks for all conference delegates and exhibition visitors will be offered. All exhibitors are welcome to also provide drinks and snacks for the attendees.

2015,

Grenoble, France

#### GENERAL INFORMATION

### **DATE Networking Event**

#### Wed, March 11, 2015

As one of the main networking opportunities during the DATE week, the DATE Party states a perfect occasion to meet friends and colleagues in a relaxed atmosphere while enjoying local amenities. It will take place on March 11, 2015, from 1930 to 2300 in the renowned "Musée de Grenoble" (Grenoble Museum).

This painting museum features a unique collection of ancient, modern and contemporary art including major masterpieces of classical Flemish, Dutch, Italian and Spanish painting and all the great pot-1945 contemporary art-trends, right up to the most recent artwork of the 2000s. During this evening, you can enjoy the famous French Cuisine and outstanding wines. Discover the region of the French Alps through its cheese and wine specialties. The dinner will be accompanied by jazz songs and instrumental music from Annah Cruz and her vocal band. Another highlight will be the show waders "THE INSEPARABLES", sweet and ephemeral characters walking through the premises, releasing dreams and laughter. Furthermore, at the very beginning of the evening, from 2000 to 2130, you will have the opportunity to visit parts of the permanent collection of the museum (ninetieth and twenties century). Please kindly note that it is not a seated dinner. All delegates, exhibitors and their guests are invited to attend the party. Please be aware that entrance is only possible with a valid party ticket. Each full conference registration includes a ticket for the DATE Party (which needs to be booked during the online registration process though). Additional tickets can be purchased on-site at the registration desk (subject to availability of tickets). Price for extra ticket: 60 € per person.

**How to get there:** Tram B has a stop called "Notre Dame Musée" which is next to the Museum. Attendees would take Tram A from Alpexpo and change for Tram B in one of the stations between "Gares" and "Maison du Tourisme" to get to the museum. The trip takes about 30 minutes.

### Interactive Presentations, sponsored by Cadence Academic Network

Interactive presentations allow presenters to interactively discuss novel ideas and work in progress that may require additional research work and discussion, with other researchers working in the same area. Interested attendees can walk around freely and talk to any author they want in a vivid face-to-face format. The author may illustrate his work with a slide shown on a laptop computer, a demonstration, etc. IP presentations will also be accompanied by a poster. Each IP will additionally be introduced in a relevant regular session prior to the IP Session in a one-minute presentation.

To give an overview, there will be one central projection displaying a list of all the presentations going on at the same time in the IP area. Interactive Presentation (IP) Sessions will be held in the Poster Area (as part of the exhibition area) in 30-minute time slots on the following days:

| IP Session 1 | Tuesday, March 10, 2015                      | Exhibition Area                 | 1600 – 1630         |

|--------------|----------------------------------------------|---------------------------------|---------------------|

| IP Session 2 | Wednesday, March 11, 2015                    | Exhibition Area                 | 1000 – 1030         |

| IP Session 3 | Wednesday, March 11, 2015                    | Exhibition Area                 | 1600 – 1630         |

|              | Thursday, March 12, 2015<br>of Best IP Award | Exhibition Area<br>Salle Oisans | 1000 - 1030<br>1315 |

| IP Session 5 | Thursday, March 12, 2015                     | Exhibition Area                 | 1530 – 1600         |

#### EXECUTIVE SESSIONS — TUESDAY

Organiser: Yervant Zorian, Synopsys, US

DATE 2015 will again feature an Executive Track of presentations by leading company executives representing a range of semiconductor manufacturers, EDA vendors, fables houses and IP providers. This one-day programme will be held on Tuesday 10 March, the first day of the DATE conference immediately after the Opening Session and it will be comprised of three sessions where the executives will present their technical/business vision in this nanometer technology era. Each session will feature 3-4 executives and run in parallel to the technical conference tracks.

All three executive sessions will first provide each executive with a timeslot to present his/her vision, followed by a question and answer period to provide interaction with the attendees. The Executive Track should offer prospective attendees valuable information about the vision and roadmaps of their corresponding companies from a business and technology point-of-view.

#### 2.1

### **EXECUTIVE SESSION:**

New Opportunities in the Internet of Things

See Page 41

#### 3.1

#### **EXECUTIVE SESSION:**

Extending Morre's Law & Heterogeneous Integration

See Page 46

#### 4.1

#### **EXECUTIVE SESSION:**

Trends and Challenges in Today's Automotive Semiconductors

See Page 52

DATE 15

March 9-13, 2015, Grenoble, France

#### SPECIAL DAY - WEDNESDAY

Organiser and Chair: Rolf Drechsler, University of Bremen/DFKI, DE

#### **Designing Electronics for the Internet of Things**

The IoT, also known as the "Internet of Anything" promises to realize the omnipresent network of tens of billions of communicating devices. These devices will enable new business models and revolutionize industrial production, logistics and social life, but they will also require dedicated hardware, ultra-low power robust devices and new design methodologies. The sessions and keynotes of the Special Day on Wednesday will cover these topics.

5.1 SPECIAL DAY Hot Topic: Applications of IoT

See Page 56

SPECIAL DAY Hot Topic: Platforms for the IoT

See Page 61

- 7. SPECIAL DAY Keynotes

- 7.0.1 Industrie 4.0: From the Internet of Things to Cyber-Physical Production Systems

- 7.0.2 The rise of IOT, and the role of EDA

- 7.0.3 Market driven challenges of IoT devices

See Page 65

7.1 SPECIAL DAY Hot Topic: Design Tools for the IoT

See Page 65

SPECIAL DAY Panel:

Security and Verification for the IoT

See Page 71

#### SPECIAL DAY — THURSDAY

Organiser and Chair: Jo De Boeck, IMEC, BE

#### **Designing Electronics for Medical Applications**

Providing universal and costly-effective healthcare to the complete human kind has become a major challenge in our modern society. Thus, Thursday will feature an outstanding set of 4 special sessions on the topic of "Game-changing innovation in health care". This Special Day includes 10 trend-setting invited papers, 8 of which come from key industrial players in the health care field and one keynote during lunch time.

9.1 SPECIAL DAY Hot Topic: Game-changing Innovative Technology Platforms for Health Care

See Page 77

SPECIAL DAY Hot Topic: Wearable Medical Applications

See Page 82

11. SPECIAL DAY Keynote

Bioelectronic Medicines – Heralding in a New

Therapeutic Approach

See Page 87

11.1 SPECIAL DAY Hot Topic: Implantable Medical Applications

See Page 87

12.1 SPECIAL DAY Hot Topic: Technology and Design Platforms for Diagnostics

See Page 93

14

March 9-13

2015,

Grenoble, France

### SPECIAL SESSIONS

Special Session Chairs: Marco Casale-Rossi, Synopsys, US Marco Platzner, University of Paderborn, DE

The following ten Special Sessions have been organized, which should prove to be of great general interest. Panel Sessions provide forums in which motivated opinions on unsettled issues are discussed. The 'trend setters' are given a time-slot to present their views, which are then subjected to critical appraisal and rich exchanges from the audience. Hot Topic Sessions give technical information about strongly emerging topics and offer a good overview and technical insight provided by leading experts in the field. Relevant issues and their importance for research and development are exposed as food for thought. Embedded Tutorials give an insight of relevant topics usually starting from an introductory basis.

3.6 Hot Topic - Memristor based Computation-in-**Memory Architecture for Data-Intensive Applications**

Organisers: Koen Bertels, TU Delft, NL

Said Hamdioui, TU Delft, NL

Hot Topic - Design Methodologies for a Cyber-3.8 Physical Systems Approach to Personalized Medicine-on-a-Chip: Challenges and Opportunities

Organiser: Krishnendu Chakrabarty, Duke University, US

5.8 Hot Topic - The Next Generation of Virtual Prototyping: Ultra-fast yet Accurate Simulation of **HW/SW Systems**

Organisers: Daniel Müller-Gritschneder, Technische Universitaet

München, DE

Oliver Bringmann, University of Tübingen, DE

6.6 Panel - The Future of Electronics, Semiconductor, and Design in Europe

Organiser: Marco Casale-Rossi, Synopsys, US

7.2 **Hot Topic - Trading Accuracy for Efficient** Computing

Organisers: Anand Raghunathan, Purdue University, US Akash Kumar, National University of Singapore, SG **Hot Topic - Advances in Hardware Trojans** Detection

Organiser: Julien Francq, Airbus Defence & Space -- CyberSecurity, FR

8.5 **Hot Topic - Spintronics based Computing**

Organisers: Weisheng Zhao, University Paris-Sud/CNRS, FR Lionel Torres, LIRMM, CNRS/University of Montpellier, FR

9.2 Hot Topic - Transparent Use of Accelerators in **Heterogeneous Computing Systems**

Organisers: Heiner Giefers, IBM Research Zurich, CH Christian Plessl, University of Paderborn, DE

9.8 Hot Topic - Monolithic 3D: A Path to Real 3D **Integrated Chips**

Organisers: Giovanni De Micheli, École Polytechnique Fédérale de

Lausanne (EPFL), CH

Pierre-Emmanuel Gaillardon, École Polytechnique Fédérale

de Lausanne (EPFL), CH

11.3 Hot Topic - Multi/Many-Core Programming: Where Are We Standing?

Organisers: Jeronimo Castrillon, Technische Universität Dresden, DE Rainer Leupers, RWTH Aachen, DE

2015,

Grenoble, France

DATE 1

#### **EVENT OVERVIEW**

#### MONDAY

- Educational Tutorials

- Fringe Meetings

- Welcome Reception

- ACM SIGDA/EDAA PhD Forum

#### TUESDAY

- Opening Plenary, DATE Awards Ceremony and Keynote Addresses

- Technical Conference

- Executive Sessions

- Lunchtime Keynote Session sponsored by Mentor Graphics

- Vendor Exhibition & Exhibition Theatre

- University Booth

- Fringe Meetings

- Exhibition Reception

#### WEDNESDAY

- Technical Conference

- Special Day on Designing Electronics for the Internet of Things and Keynotes

- Vendor Exhibition & Exhibition Theatre

- University Booth

- DATE Networking Event (DATE Party)

#### THURSDAY

- Technical Conference

- Special Day on Designing Electronics for Medical Applications and Keynote

- Vendor Exhibition & Exhibition Theatre

- University Booth

- Fringe Meetings

#### FRIDAY

Special Interest Workshops

#### CONTACTS

#### **DATE 2015 Event Secretariat**

c/o K.I.T. Group GmbH Dresden Muenzgasse 2

01067 Dresden, Germany

Phone: +49 351 4967 541 Fax: +49 351 4956 116 E-Mail: date@kitdresden.de

#### **Conference & Exhibition Manager**

Franziska Kremling K.I.T. Group GmbH, DE

Phone: +49 351 4967 541

#### **Registration & Accommodation**

Eva Schubert

K.I.T. Group GmbH, DE

Phone: +49 351 4967 312

#### MONDAY 09 MARCH

| 0730 -<br>0930 | Tutorial Registration and Welcome Refreshments                                                                                      |                                                                                                                                            |                                                                   |                                                                                                                            |                                                                                                             |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| Breaks         |                                                                                                                                     | orning Coffee Bro<br>ernoon Coffee B                                                                                                       |                                                                   |                                                                                                                            |                                                                                                             |  |

|                | Belle-Etoile                                                                                                                        | Meije                                                                                                                                      | Chartreuse                                                        | Sept Laux                                                                                                                  | Les Bans                                                                                                    |  |

| 0930-<br>1300  | M01<br>New<br>Technologies:<br>Spintronics:<br>From Devices<br>To Systems                                                           | M03<br>Embedded<br>Systems:<br>Embedded<br>Memory<br>Design<br>for Future<br>Technologies:<br>Challenges,<br>Solutions and<br>Applications | M05<br>Automotive:<br>Let's kick<br>start electric<br>vehicles!   | M07<br>Low Power:<br>Fixed-point<br>refinement, a<br>guaranteed<br>approach<br>towards<br>energy<br>efficient<br>computing | M09 Testing: From Data to Actions: Applications of Data Analytics in Semi- conductor Manufac- turing & Test |  |

| 1300 –<br>1430 | Lunch Break                                                                                                                         |                                                                                                                                            |                                                                   |                                                                                                                            |                                                                                                             |  |

| 1330           | Conference reg                                                                                                                      | gistration begins                                                                                                                          |                                                                   |                                                                                                                            |                                                                                                             |  |

|                | Belle-Etoile                                                                                                                        | Meije                                                                                                                                      | Chartreuse                                                        | Sept Laux                                                                                                                  | Les Bans                                                                                                    |  |

| 1430 —<br>1800 | M02<br>New<br>Technologies:<br>Spin Orbit<br>Torque<br>Magnetic<br>Memories<br>(SOT-MRAM):<br>A Device to<br>Architecture<br>Review | M04<br>Embedded<br>Systems:<br>Functional<br>Qualification:<br>Applications<br>in the C/C++<br>domain                                      | M06<br>Automotive:<br>Automotive<br>Cyber-<br>Physical<br>Systems | M08<br>Low Power:<br>The power<br>of Power<br>in future<br>wireless<br>smart<br>systems for<br>the Internet of<br>Things   | M10<br>Testing:<br>Memory Test<br>and Reliability<br>in Nano-Era                                            |  |

| 1800 —<br>1900 | Walaama Pagantian Calla da Pagantian                                                                                                |                                                                                                                                            |                                                                   |                                                                                                                            |                                                                                                             |  |

ACM SIGDA/EDAA PhD Forum, Salle de Reception

1900 -

2100

18

#### TUESDAY 10 MARCH TUESDAY 10 MARCH 0730 Registration and speaker's breakfast, room Les Écrins Registration and speaker's breakfast, room Les Écrins 0730 0830-0830-1.1 Opening Session: Plenary, Awards Ceremony & Keynote Addresses 1.1 Opening Session: Plenary, Awards Ceremony & Keynote Addresses 1030 1030 1030 -1030 -**Exhibition and Coffee Break Exhibition and Coffee Break** 1130 1130 TRACK 1 TRACK 2 TRACK 3 TRACK 4 TRACK 5 TRACK 6 TRACK 7 TRACK 8 Oisans Belle-Etoile Stendhal Lesdiguières Chartreuse Meije Bavard Les Bans 1130 -2.1 2.2 2.3 2.4 2.5 2.6 2.7 2.8 1130 -1300 New Adaptability System Level Automotive Power of Design and Compilation Facilities for 1300 Opportunities in for Low Power Design Methods Systems and Assertions Analysis of and Code Design and the Internet of Smart Energy Dependable Transformations Fabrication for Computing Things Systems Systems FDS011C Reconfigurable Computing 1300 -1300 -Lunch Break Lunch Break 1430 1430 Keynote session sponsored by Mentor Graphics, 1320-1420, room Oisans Keynote session sponsored by Mentor Graphics, 1320-1420, room Oisans Oisans Belle-Etoile Stendhal Chartreuse Meije Bavard Les Bans Lesdiguières 3.5 1430 -3.2 3.3 3.4 3.6 3.7 1430 -1600 Extending Passive Loop Acceleration Tackling Breaking Hot Topic -Model-based Hot Topic - Design 1600 Memory Walls Simulation Methodologies Morre's Law & Implementation Memristor based Analysis and Heterogeneous Attacks and with Emerging **Boundaries** Computation-Verification for a Cyber-Countermeasures Architectures and in-Memory Physical Systems Integration Technologies Architecture for Approach to Data-Intensive Personalized **Applications** Medicine-on-a-Chip: Challenges and Opportunities 1600 -1600 -1700 1700 Coffee Break Coffee Break **IP1 Interactive Presentations IP1 Interactive Presentations** Belle-Etoile Stendhal Oisans Chartreuse Meije Bayard Les Bans Lesdiguières 1700 -4.2 4.4 4.5 4.6 4.7 4.8 1700 -Online Testing 1830 Trends and Implementation Multi-/Manycore Exploring Industrial Test **How Resilient** Strength by 1830 Challenges and Verification Schedulina Reliability and and Validation and Reliable Are Emerging Interdisciplinary in Today's of Security Efficiency Experiments Memories Technologies? Research: Tradeoffs at the The Cadence Automotive Components Semiconductors Architectural Academic Level Network

EXHIBITION RECEPTION

DATE

OI 7

March 9

France

TUE

1830 -

1930

1830 -

1930

**EXHIBITION RECEPTION**

### WEDNESDAY 11 MARCH

| 0730           | Registration and speaker's breakfast, room Les Écrins                    |                                                                      |                                                                    |                                                                                          |  |  |

|----------------|--------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|

|                | TRACK 1                                                                  | TRACK 2                                                              | TRACK 3                                                            | TRACK 4                                                                                  |  |  |

|                | Salle Oisans                                                             | Belle-Etoile                                                         | Stendhal                                                           | Chartreuse                                                                               |  |  |

| 0830-<br>1000  | 5.1<br>SPECIAL DAY<br>Hot Topic:<br>Applications<br>of IoT               | 5.2<br>Hardware Trojan<br>and Active<br>Implementation<br>Attacks    | 5.3<br>Variability<br>Challenges<br>in Nanoscale<br>Circuits       | 5.4<br>Emerging<br>Technologies for<br>NoCs                                              |  |  |

| 1000 –<br>1100 |                                                                          |                                                                      | Break<br>Presentations                                             |                                                                                          |  |  |

|                | Salle Oisans                                                             | Belle-Etoile                                                         | Stendhal                                                           | Chartreuse                                                                               |  |  |

| 1100 –<br>1230 | 6.1<br>SPECIAL DAY Hot<br>Topic: Platforms<br>for the IoT                | 6.2<br>Physical<br>Unclonable<br>Functions                           | 6.3<br>Emerging<br>Low Power<br>Techniques                         | 6.4<br>Bridging the<br>Moore's Law Gap<br>with Application-<br>Specific<br>Architectures |  |  |

| 1230 –<br>1430 | 7.0 SF                                                                   | Lunch<br>PECIAL DAY Keynotes                                         | Break<br>s, 1250 – 1420, room (                                    | Disans                                                                                   |  |  |

|                | Salle Oisans                                                             | Belle-Etoile                                                         | Stendhal                                                           | Chartreuse                                                                               |  |  |

| 1430 –<br>1600 | 7.1<br>SPECIAL DAY<br>Hot Topic: Design<br>Tools for the IoT             | 7.2<br>Hot Topic -<br>Trading Accuracy<br>for Efficient<br>Computing | 7.3<br>Hot Topic -<br>Advances in<br>Hardware Trojans<br>Detection | 7.4<br>Routing Advances<br>for Fault-tolerant<br>and Multicast<br>NoCs                   |  |  |

| 1600 –<br>1700 | Coffee Break<br>IP3 Interactive Presentations                            |                                                                      |                                                                    |                                                                                          |  |  |

|                | Salle Oisans                                                             | Belle-Etoile                                                         | Stendhal                                                           | Chartreuse                                                                               |  |  |

| 1700 –<br>1830 | 8.1<br>SPECIAL DAY<br>Panel: Security<br>and Verification<br>for the IoT | 8.2<br>Flash Memories<br>& Numerical<br>Approximation                | 8.3<br>Dynamic Thermal<br>Management for<br>Multi-cores            | 8.4<br>Industrial<br>System Design<br>Opportunities                                      |  |  |

| 1930 –<br>2300 | DATE Networking Event (DATE PARTY)                                       |                                                                      |                                                                    |                                                                                          |  |  |

| WEDNESDAY | 11 | MARC |

|-----------|----|------|

|-----------|----|------|

| V                                                                    | VEDIVESI                                                                               | JAY TIIV                                                            | //ARCH                                                                                                                                 |                |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Regist                                                               | ration and speaker's                                                                   | breakfast, room Les                                                 | Écrins                                                                                                                                 | 0730           |

| TRACK 5                                                              | TRACK 6                                                                                | TRACK 7                                                             | TRACK 8                                                                                                                                |                |

| Meije                                                                | Bayard                                                                                 | Les Bans                                                            | Lesdiguières                                                                                                                           |                |

| 5.5<br>Critical Embedded<br>Systems                                  | 5.6<br>Analyzing and<br>Improving<br>Memories                                          | 5.7<br>Architectures<br>and Design for<br>Cyber-Physical<br>Systems | 5.8<br>Hot Topic - The<br>Next Generation<br>of Virtual<br>Prototyping: Ultra-<br>fast yet Accurate<br>Simulation of HW/<br>SW Systems | 0830-<br>1000  |

|                                                                      |                                                                                        | Break<br>Presentations                                              |                                                                                                                                        | 1000 –<br>1100 |

| Meije                                                                | Bayard                                                                                 | Les Bans                                                            | Lesdiguières                                                                                                                           |                |

| 6.5<br>Multimedia<br>and Consumer<br>Electronics                     | 6.6 Panel – The Future of Electronics, Semiconductor, and Design in Europe             | 6.7<br>Application-<br>Mapping<br>Strategies for<br>Many-Cores      | 6.8 → 6.6<br>in room Bayard                                                                                                            | 1100 –<br>1230 |

| 7.0 SP                                                               |                                                                                        | Break<br>s, 1250 – 1420, room (                                     | Disans                                                                                                                                 | 1230 —<br>1430 |

| Meije                                                                | Bayard                                                                                 | Les Bans                                                            | Lesdiguières                                                                                                                           |                |

| 7.5<br>System Reliability:<br>from Runtime<br>to Design<br>Languages | 7.6<br>Test Power<br>and 3-D Fault<br>Tolerance                                        | 7.7<br>Energy-efficient<br>Computing                                | 7.8<br>Critical Research<br>Areas Driven<br>by Industry<br>Transformations                                                             | 1430 —<br>1600 |

| Coffee Break<br>IP3 Interactive Presentations                        |                                                                                        |                                                                     |                                                                                                                                        |                |

| Meije                                                                | Bayard                                                                                 | Les Bans                                                            | Lesdiguières                                                                                                                           |                |

| 8.5<br>Hot Topic -<br>Spintronics based<br>Computing                 | 8.6<br>Statistical<br>Answers to<br>Analog/Mixed<br>Signal Design and<br>Test Problems | 8.7<br>Compilers<br>and Tools for<br>Performance                    | 8.8<br>Share a Fab -<br>Multi Project<br>Wafers Enable<br>Your Innovations                                                             | 1700 –<br>1830 |

|                                                                      |                                                                                        |                                                                     | _                                                                                                                                      |                |

EXHIBITION THEATRE

T-TRACK

A-TRACK

E-TRACK

DATE Networking Event (DATE PARTY)

DATE 15

1930 –

2300

March 9—13, 2015, Grenoble, France

| THURSD | AY 12 | MARCH |

|--------|-------|-------|

|--------|-------|-------|

| 0730           | Registration and speaker's breakfast, room Les Écrins                                                         |                                                                                                                       |                                                                                      |                                                                                    |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|

|                | TRACK 1                                                                                                       | TRACK 2                                                                                                               | TRACK 3                                                                              | TRACK 4                                                                            |  |  |  |

|                | Salle Oisans                                                                                                  | Belle-Etoile                                                                                                          | Stendhal                                                                             | Chartreuse                                                                         |  |  |  |

| 0830-<br>1000  | 9.1<br>SPECIAL DAY<br>Hot Topic:<br>Game-changing<br>Innovative<br>Technology<br>Platforms for<br>Health Care | 9.2<br>Hot Topic -<br>Transparent Use<br>of Accelerators<br>in Heterogeneous<br>Computing<br>Systems                  | 9.3<br>NoC Optimization                                                              | 9.4<br>Advanced Trends<br>in Alternative<br>Technologies                           |  |  |  |

| 1000 —<br>1100 |                                                                                                               |                                                                                                                       | Break<br>Presentations                                                               |                                                                                    |  |  |  |

|                | Salle Oisans                                                                                                  | Belle-Etoile                                                                                                          | Stendhal                                                                             | Chartreuse                                                                         |  |  |  |

| 1100 –<br>1230 | 10.1<br>SPECIAL DAY Hot<br>Topic: Wearable<br>Medical<br>Applications                                         | 10.2<br>Emerging Memory<br>Architectures                                                                              | 10.3<br>Modern<br>Architectures<br>for Real-Time<br>Systems                          | 10.4<br>Energy Aware<br>Data Center:<br>Design and<br>Management                   |  |  |  |

| 1230 —<br>1400 |                                                                                                               | Lunch Break<br>Best IP Award Presentation, 1315-1320, room Oisans<br>11.0 SPECIAL DAY Keynote, 1320-1350, room Oisans |                                                                                      |                                                                                    |  |  |  |

|                | Salle Oisans                                                                                                  | Belle-Etoile                                                                                                          | Stendhal                                                                             | Chartreuse                                                                         |  |  |  |

| 1400 –<br>1530 | 11.1<br>SPECIAL DAY Hot<br>Topic: Implantable<br>Medical<br>Applications                                      | 11.2<br>Variability and<br>Robustness<br>for Emerging<br>Technologies                                                 | 11.3<br>Hot Topic - Multi/<br>Many-Core<br>Programming:<br>Where Are We<br>Standing? | 11.4<br>Logic Synthesis:<br>the Faithful, the<br>Approximate and<br>the Stochastic |  |  |  |

| 1530 –<br>1600 | Coffee Break<br>IP5 Interactive Presentations                                                                 |                                                                                                                       |                                                                                      |                                                                                    |  |  |  |

|                | Salle Oisans                                                                                                  | Belle-Etoile                                                                                                          | Stendhal                                                                             | Chartreuse                                                                         |  |  |  |

| 1600 –<br>1730 | 12.1<br>SPECIAL DAY Hot<br>Topic: Technology<br>and Design<br>Platforms for<br>Diagnostics                    | 12.2<br>Solver Advances<br>and Emerging<br>Applications                                                               | 12.3<br>Patterning,<br>Pairing,<br>Placement and<br>Packing                          | 12.4<br>High-Level<br>Specifications<br>and Models                                 |  |  |  |

| <br>    | <br>    | 40 |           |     |

|---------|---------|----|-----------|-----|

| =11 11: | <br>)AY | 12 | N / N / N | יטי |

|         |         |    |           |     |

| Registration and speaker's breakfast, room Les Écrins 0730             |                                                                                                                        |                                                                                                |                                                                                                 |                |  |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------|--|

| TRACK 5                                                                | TRACK 6                                                                                                                | TRACK 7                                                                                        | TRACK 8                                                                                         |                |  |

| Meije                                                                  | Bayard                                                                                                                 | Les Bans                                                                                       | Lesdiguières                                                                                    |                |  |

| 9.5<br>Modeling and<br>Simulation of<br>Extra-Functional<br>Properties | 9.6<br>Design, Synthesis<br>and Validation of<br>Analog Circuits                                                       | 9.7<br>Test Generation,<br>Fault Simulation<br>and Diagnosis                                   | 9.8<br>Hot Topic -<br>Monolithic 3D: A<br>Path to Real 3D<br>Integrated Chips                   | 0830-<br>1000  |  |

|                                                                        |                                                                                                                        | Break<br>Presentations                                                                         |                                                                                                 | 1000 –<br>1100 |  |

| Meije                                                                  | Bayard                                                                                                                 | Les Bans                                                                                       | Lesdiguières                                                                                    |                |  |

| 10.5<br>Reconfigurable<br>Architectures and<br>Applications            | 10.6<br>Circuit Design<br>and Test: From<br>Characterization<br>to Measurement                                         | 10.7<br>Expanding the<br>Applicability of<br>Formal Methods                                    | 10.8<br>From IP to EDA<br>Tools Enterprise<br>Management:<br>What is so<br>special?             | 1100 –<br>1230 |  |

|                                                                        | Lunch<br>P Award Presentation<br>SPECIAL DAY Keynot                                                                    |                                                                                                |                                                                                                 | 1230 –<br>1400 |  |

| Meije                                                                  | Bayard                                                                                                                 | Les Bans                                                                                       | Lesdiguières                                                                                    |                |  |

| 11.5<br>Ultra-low Power<br>Devices for Health<br>and Rehabilitation    | 11.6<br>Video<br>Architectures for<br>Multimedia and<br>Communications                                                 | 11.7<br>Exploiting Dark<br>Silicon                                                             | 11.8 (1400-1500) Exhibition Keynote: Designing Systems for the Connected Autonomous Future      | 1400 –<br>1530 |  |

| Coffee Break<br>IP5 Interactive Presentations                          |                                                                                                                        |                                                                                                |                                                                                                 |                |  |

| Meije                                                                  | Bayard                                                                                                                 | Les Bans                                                                                       | Lesdiguières                                                                                    |                |  |

| 12.5<br>New Perspectives<br>in Next-<br>Generation<br>Medical Systems  | 12.6<br>Medical Design<br>Automation: Is All<br>That Simulation<br>and Model<br>Reduction Getting<br>Into Your "Head"? | 12.7<br>Brain Health and<br>Mental Disorders:<br>new challenges<br>for electronic<br>engineers | 12.8 (1500-1730) Tutorial: An Industry Approach to FPGA/ARM System Development and Verification | 1600 –<br>1730 |  |

D-TRACK SPECIAL SESSION E-TRACK EXHIBITION THEATRE

A-TRACK T-TRACK

25

Ħ

#### Z O N

### FRIDAY 13 MARCH

| 0730 –<br>0830 Workshop Registration and Welcome Refreshments                                                    |                                                                         |                                                                                                  |                                                                                                      |                                                                                                               |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Breaks Please see individual workshop programmes for lunch and break times                                       |                                                                         |                                                                                                  |                                                                                                      |                                                                                                               |

| 0830 – 1600<br>Meije                                                                                             | 0830-1630<br>Bayard                                                     | 0830 – 1600<br>Stendhal                                                                          | 0830-1630<br>Berlioz                                                                                 | 0815-1730<br>Belle-Etoile                                                                                     |

| W01<br>1st Workshop<br>on Model-<br>Implementation<br>Fidelity (MiFi)                                            | W02<br>Design<br>Automation<br>of Things: EV<br>Battery Packs           | W03 2nd International Workshop on Neuromorphic and Brain- Based Computing Systems (NeuComp 2015) | W04 DUHDe – 2nd Workshop on Design Automation for Understanding Hardware Designs                     | W05<br>3D Integration<br>Technology,<br>Architecture,<br>Design,<br>Package,<br>Automation, and<br>Test       |

| 0830 – 1700<br>Chartreuse                                                                                        | 0830-1630<br>Salle<br>Lesdiguières                                      | 0830 – 1700<br>Sept Laux 4                                                                       | 0830 – 1630<br>Sept Laux 5                                                                           | 0830 – 1700<br>Les Bans                                                                                       |

| W06<br>Workshop on<br>Manufacturable<br>and Dependable<br>Multicore<br>Architectures<br>at Nanoscale<br>(MEDIAN) | W07<br>Designing with<br>Uncertainty -<br>Opportunities &<br>Challenges | W08 Heterogeneous Architectures and Design Methods for Embedded Image Systems                    | W09 International Workshop on Optical/Photonic Interconnects for Computing Systems (OPTICS Workshop) | W10<br>TRUDEVICE<br>2015: Workshop<br>on Trustworthy<br>Manufacturing<br>and Utilization of<br>Secure Devices |

### TUTORIALS - MONDAY 09 MARCH

| 0730-0930         | REGISTRATION AND TUTORIAL WELCOME REFRESHMENTS                                                           |

|-------------------|----------------------------------------------------------------------------------------------------------|

| 0930-1300         | TUTORIALS (1100-1130 Coffee Break)                                                                       |

| MO1 Belle-Etoile  | NEW TECHNOLOGIES: SPINTRONICS: FROM DEVICES TO SYSTEMS                                                   |

| MO3 Meije         | EMBEDDED SYSTEMS: EMBEDDED MEMORY DESIGN FOR FUTURE TECHNOLOGIES: CHALLENGES, SOLUTIONS AND APPLICATIONS |

| MO5 Chartreuse    | AUTOMOTIVE: LET'S KICK START ELECTRIC VEHICLES!                                                          |

| MO7 Sept Laux     | LOW POWER: FIXED-POINT REFINEMENT, A GUARANTEED APPROACH TOWARDS ENERGY EFFICIENT COMPUTING              |

| MO9 Les Bans      | TESTING: FROM DATA TO ACTIONS: APPLICATIONS OF DATA ANALYTICS IN SEMICONDUCTOR MANUFACTURING & TEST      |

| 1300-1430<br>1330 | LUNCH BREAK CONFERENCE REGISTRATION BEGINS                                                               |

| 1430-1800         | TUTORIALS (1600-1630 Coffee Break)                                                                       |

| MO2 Belle-Etoile  | NEW TECHNOLOGIES: SPIN ORBIT TORQUE<br>MAGNETIC MEMORIES (SOT-MRAM): A DEVICE TO<br>ARCHITECTURE REVIEW  |

| МО4 Меіје         | EMBEDDED SYSTEMS: FUNCTIONAL QUALIFICATION: APPLICATIONS IN THE C/C++ DOMAIN                             |

| MO6 Chartreuse    | AUTOMOTIVE: AUTOMOTIVE CYBER-PHYSICAL SYSTEMS                                                            |

| MO8 Sept Laux     | LOW POWER: THE POWER OF POWER IN FUTURE WIRELESS SMART SYSTEMS FOR THE INTERNET OF THINGS                |

| M10 Les Bans      | TESTING: MEMORY TEST AND RELIABILITY IN NANO-ERA                                                         |

| 1800-1900         | WELCOME RECEPTION                                                                                        |

ACM SIGDA /EDAA PHD FORUM

1900-2100

March 9-13

2015

Grenoble,

#### **TUTORIALS**

MO1

## New Technologies: Spintronics: From Devices To Systems

Belle-Etoile 0930 - 1300

Organiser |

Rangharajan Venkatesan, Purdue, US

**Invited Speakers**

Kaushik Roy, Purdue University, US Anand Raghunathan, Purdue University, US Rangharajan Venkatesan, Purdue, US

With the scaling of CMOS technology approaching its fundamental limits, several new technologies are being actively explored as potential replacements. Among them, spintronics, which uses electron "spin" rather than "charge" as a state variable is considered to be a promising direction for the post-CMOS era. Spintronic devices are well-suited for realizing memories that are highly dense and non-volatile, i.e., have very low leakage power, compared to their CMOS counterparts such as SRAM and DRAM, and therefore have great potential to revolutionize the storage and computing capabilities of future systems. Further, spintronic devices have certain unique characteristics that make them highly efficient for non-Boolean computing. In addition to extensive research efforts over the decade, multiple industrial prototypes and early commercial offerings of spintronic memories underscore the great interest in this field.

This tutorial presents a devices-to-systems overview of the state-of-the-art in the design of spintronic computing systems. The first part of the tutorial focuses on the design of memory hierarchies with different spintronic technologies — Spin Transfer Torque Magnetic RAM (STI-MRAM). Domain Wall Memory (DWM), Spin-Hall Magnetic RAM (SH-MRAM). We show that spintronic memories fundamentally change the design landscape in terms of read-write stability, density, energy, and performance and pose certain unique challenges such as high write latency and energy, asymmetry in write operations, variable access latency, etc. We survey a wide range of device, circuit and architectural techniques to address the challenges associated with spintronic memories.

The second part of this tutorial focuses on the design of spintronic logic. Realizing Boolean logic with spintronic devices is considerably more challenging than memory. We will describe various proposals for spintronic Boolean logic families and compare their merits and demerits with CMOS. Re-configurable fabrics, which make extensive use of memory to store logic functions and interconnect configurations, offer an opportunity to harness the efficiency of spintronic memory for logic design. This tutorial will cover proposals for spintronic reconfigurable fabrics and memory-based computing. Further, spintronic devices are highly promising in certain application domains that match their characteristics. We present one such application - neuromorphic computing, the design of computing systems that mimic the functionality of the human brain. Neuromorphic computing has received great interest in the last decade in several applications involving classification, recognition, search, and inference and is used in real-world systems such as Google+ image search, Apple Siri voice recognition, etc. We describe recent efforts to use spintronic devices for realizing the building blocks of artificial neural networks, viz. neurons and synapses, and to utilize these primitives for large-scale neuromorphic computing.

0930 SESSION 1

□93□ INTRODUCTION TO SPINTRONICS

Speaker: Kaushik Roy, Purdue University, US

1000 SPINTRONIC MEMORIES: DEVICES AND BIT-CELLS

Speaker: Kaushik Roy, Purdue University, US

1045 SPINTRONIC MEMORY HIERARCHIES

Speaker: Rangharajan Venkatesan, Purdue, US

1200 SESSION 2

1200 SPINTRONIC LOGIC DEVICES

Speaker: Kaushik Roy, Purdue University, US

1220 BOOLEAN AND NON-BOOLEAN COMPUTING WITH

SPINTRONIC DEVICES

Speaker: Anand Raghunathan, Purdue University, US

M02

#### New Technologies: Spin Orbit Torque Magnetic Memories (SOT-MRAM): A Device to Architecture Review

Belle-Etoile 1430 - 1800

Organiser Mehdi Tahoori, Karlsruhe Institute of Technology, DE

Invited Speakers

Pietro Gambardella, Department of Materials, ETH Zurich, CH Gregory Di Pendina and Guillaume Prenat, Spintec / CEA-CNRS, FR Mehdi Tahoori, Karlsruhe Institute of Technology, DE