Alpes Congrès, Grenoble, France March 14 - 18, 2011

Design, Automation & Test in Europe

The European System Design Show From Systems-on-Chip to Embedded Computing

www.date-conference.com

# Welcome to DATE 11

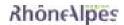

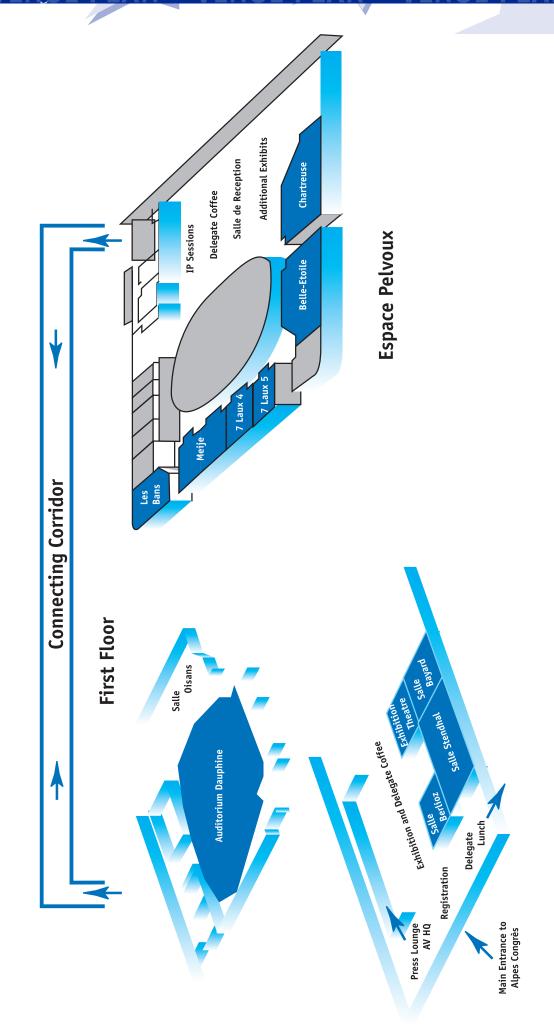

In this exhibition guide you will find listings of exhibitors contact details and their products being demonstrated on the exhibition floor. The classified product finder will help you locate the right solution within the show; maps and plans of Alpexpo, exhibition hall and additional exhibition space will also help you to get around.

# FREE - ENTRY to KEYNOTE SESSIONS & EXHIBITION THEATRE (see p.8) & SPECIAL EVENTS!

## **OPENING PLENARY KEYNOTES –**

0830-1030, Tuesday 15 March, Auditorium Dauphine

Biologically-inspired massively-parallel architectures— computing beyond a million processors

S Furber, ICL Professor of Computer Engineering, School of Computer Science, Manchester U, United Kingdom

How technology R&D leadership brings a competitive advantage in the fields of multimedia convergence and power applications

Philippe Magarshack, Group Vice-President, Technology R&D - General Manager, Central CAD and Design Solutions, STMicroelectronics, France

# LUNCH AND LEARN SESSION SPONSORED BY MENTOR GRAPHICS

1300-1400, Tuesday 15 March, Auditorium Dauphine Grenoble EDA Ecosystem - From Research to Market

# SPECIAL DAY KEYNOTE - WIRELESS INNOVATIONS FOR SMARTPHONES

1400-1430, Wednesday 16 March, Room Oisans Hannu Kauppinen, Director, Head of Radio Systems Laboratory, Nokia Research Center, Finland

# SPECIAL DAY KEYNOTE - SMART ENERGY AT ST

1330-1400, Thursday 17 March, Room Oisans Carmelo Papa, Executive VP Industrial and Multisegment, STMicroelectronics, Italy

| CONTENTS                     | contents |

|------------------------------|----------|

| At-a-Glance Timetable        | 4        |

| Conference Highlights        | 5        |

| Exhibition Theatre Programme | 8        |

| DATE 11 Commercial sponsors  | 12       |

| Media Partners               | 13       |

| Tool Seminars                | 14       |

| Venue Plan                   | 15       |

| Exhibition Floorplan         | 16-17    |

| Exhibitor List               | 18       |

| Exhibitor Listings           | 19       |

| Call for Papers              | 36       |

# Exhibition Opening Times:

Tuesday 15 March

1000 - 1830\*

(\*Evening Reception offered by

the City of Grenoble

Wednesday 16 March 1000 - 1800

from 1830 - 1930hrs)

Thursday 17 March 1000 - 1700

**Entrance to the Exhibition is FREE**

#### **DATE Event Secretariat**

European Conferences 3 Coates Place Edinburgh EH3 7AA, UK

T: +44 (0)131 225 2892 E: sue.menzies@ec.u-net.com or E: claire.cartwright@ec.u-net.com W: www.date-conference.com

|                                                                                           | <b>₽</b> *TUE                                                                                   | SDAY                                                                                          | <ul><li>TUES</li></ul>                                       | DAY •                                                                                                                                    | TUES                                                        | DAY •                                                                            | tuesday :                                                    | 15 march                                                                                               |  |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| 0730                                                                                      | REGISTRATION & S                                                                                | SPEAKERS' BREAKFAS                                                                            | BREAKS 1030-                                                 | 1130 Exhibition Break                                                                                                                    | , 1300-1430 Lunch, 1600                                     | 0-1700 Exhibition Brea                                                           | k (1600-1630 IP1)                                            |                                                                                                        |  |

| 0830 1.1 PLENARY: OPENING, KEYNOTE ADDRESSES AND AWARDS PRESENTATION, Auditorium Dauphine |                                                                                                 |                                                                                               |                                                              |                                                                                                                                          |                                                             |                                                                                  |                                                              |                                                                                                        |  |

|                                                                                           | SPECIAL TRACK                                                                                   | EMERGING TECHNOLOGIES                                                                         | APPLICATIONS                                                 | DESIGN TECHNOLOGY                                                                                                                        | TEST                                                        | EMBEDDED SOFTWARE                                                                | SYSTEM DESIGN                                                | SPECIAL SESSIONS                                                                                       |  |

|                                                                                           | Room - Oisans                                                                                   | Room – Meije                                                                                  | Room – Belle-Etoile                                          | Room – Stendhal                                                                                                                          | Room – Chartreuse                                           | Room – Bayard                                                                    | Room – Les Bans                                              | Exhibition Theatre                                                                                     |  |

| 1130<br>to<br>1300                                                                        | 2.1<br>EXECUTIVE SESSION – Ideas<br>on Future of EDA and IP<br>Industry                         | 2.2<br>System-Level Techniques to<br>Handle Performance,<br>Reliability and Thermal<br>Issues | 2.3<br>Modelling and Simulation of<br>Interconnects          | 2.4 PANEL AND EMBEDDED<br>TUTORIAL SESSION – Logic<br>Synthesis and Place and Route:<br>After 20 Years of Engagement,<br>Wedding in View | 2.5<br>Transient Faults and Soft<br>Errors                  | 2.6<br>Networked Embedded<br>Systems                                             | 2.7<br>Design of Energy-Efficient<br>and Automotive Systems  | 2.8 EMBEDDED TUTORIAL  - Addressing Critical Power Management Verification Issues in Low Power Designs |  |

| 1400                                                                                      | 3.0 SPECIAL LUNG                                                                                | CH-TIME SESSION 1300-14                                                                       | 00 Grenoble EDA Ecosyste                                     | n Session - From Research                                                                                                                | to Market sponsored by M                                    | entor Graphics, Auditoriu                                                        | m Dauphine                                                   | _                                                                                                      |  |

|                                                                                           | Room – Oisans                                                                                   | Room – Meije                                                                                  | Room – Belle-Etoile                                          | Room – Stendhal                                                                                                                          | Room – Chartreuse                                           | Room – Bayard                                                                    | Room – Les Bans                                              | Exhibition Theatre                                                                                     |  |

| 1430<br>to<br>1600                                                                        | 3.1<br>EXECUTIVE SESSION – 22nm<br>Challenges and<br>Wealth/Knowledge Creation<br>Opportunities | 3.2<br>Power Optimisation of<br>Multi-Core Architectures                                      | 3.3<br>Core Algorithms for Formal<br>Verification Engines    | 3.4<br>Predicting Bugs and<br>Generating Tests for<br>Validation                                                                         | 3.5<br>Timing Related Issues in<br>Test                     | 3.6<br>Performance and Timing<br>Analysis                                        | 3.7<br>Implementations for<br>Digital Baseband<br>Processing | 3.8 PANEL SESSION –<br>Power Formats: Beyond<br>UPF and CPF                                            |  |

|                                                                                           | Room - Oisans                                                                                   | Room – Meije                                                                                  | Room – Belle-Etoile                                          | Room – Stendhal                                                                                                                          | Room – Chartreuse                                           | Room – Bayard                                                                    | Room – Les Bans                                              | Exhibition Theatre                                                                                     |  |

| 1700<br>to<br>1830                                                                        | 4.1<br>EXECUTIVE SESSION –<br>System Level Complexity<br>and Innovation                         | 4.2<br>Robust and Low Power<br>Systems                                                        | 4.3<br>Formal Verification<br>Techniques and<br>Applications | 4.4<br>System Level Simulation<br>and Validation                                                                                         | 4.5<br>Advances in Analogue,<br>Mixed Signal and RF Testing | 4.6 Design Automation Methodologies and Architectures for Three- Dimensional ICs | 4.7<br>Resource Management for<br>QoS Guaranteed NoCs        | SEE WEB OR EVENT GUIDE<br>FOR LATEST EXHIBITION<br>PROGRAMME                                           |  |

| 1830                                                                                      | Evening Reception                                                                               | Offered by the City of                                                                        | Grenoble                                                     |                                                                                                                                          |                                                             |                                                                                  |                                                              |                                                                                                        |  |

|                                                                                           | ≠ <b>ĕ</b> WE                                                                                   | BNESI                                                                                         | DAY • I                                                      | WEDNE                                                                                                                                    | ESDAY                                                       | • WEW                                                                            | ednesday 2                                                   | 16 march                                                                                               |  |

| 0730                                                                                      | REGISTRATION & S                                                                                | SPEAKERS' BREAKFAS                                                                            | BREAKS 1000-                                                 | 1100 Exhibition Break                                                                                                                    | , (1000-1030 IP2), 1230-                                    | 1340 Lunch, 1600-1700                                                            | Exhibition Break (1600                                       | 0-1630 IP3)                                                                                            |  |

|                                                                                           | SPECIAL TRACK                                                                                   | EMERGING TECHNOLOGIES                                                                         | APPLICATIONS                                                 | DESIGN TECHNOLOGY                                                                                                                        | TEST                                                        | EMBEDDED SOFTWARE                                                                | SYSTEM DESIGN                                                | SPECIAL SESSIONS                                                                                       |  |

|                                                                                           | Room – Oisans                                                                                   | Room – Meije                                                                                  | Room – Belle-Etoile                                          | Room - Stendhal                                                                                                                          | Room – Chartreuse                                           | Room - Bayard                                                                    | Room – Les Bans                                              | Exhibition Theatre                                                                                     |  |

| กดวก                                                                                      | F 1                                                                                             | E 2                                                                                           | E 2                                                          | E /                                                                                                                                      |                                                             | E 6                                                                              | 6.7                                                          | EVUIDITION                                                                                             |  |

| 0730 | REGISTRATION & SPEAKERS' BREAKFAST BREAKS 1000-1100 Exhibition Break, (1000-1030 IP2), 1230-1340 Lunch, 1600-1700 Exhibition Break (1600-1630 IP3) |                                                                    |                                                                          |                                                                |                                                                                     |                                                                             |                                                                                                                      |                                                                               |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|

|      | SPECIAL TRACK                                                                                                                                      | EMERGING TECHNOLOGIES                                              | APPLICATIONS                                                             | DESIGN TECHNOLOGY                                              | TEST                                                                                | EMBEDDED SOFTWARE                                                           | SYSTEM DESIGN                                                                                                        | SPECIAL SESSIONS                                                              |  |  |

|      | Room – Oisans                                                                                                                                      | Room – Meije                                                       | Room – Belle-Etoile                                                      | Room – Stendhal                                                | Room – Chartreuse                                                                   | Room - Bayard                                                               | Room – Les Bans                                                                                                      | Exhibition Theatre                                                            |  |  |

|      | 5.1<br>SMART DEVICES EMBEDDED<br>TUTORIAL –Smart Devices<br>for the Cloud Era                                                                      | 5.2<br>An Encyclopedia of Routing                                  | 5.3<br>Temperature and Variation<br>Aware Design in Low Power<br>Systems | 5.4<br>Advanced NoC Tooling and<br>Architectures               | 5.5<br>INDUSTRIAL 1                                                                 | 5.6<br>Analysis, Compilation and<br>Runtime Techniques                      | 5.7<br>EMBEDDED TUTORIAL –<br>Architectures for Online<br>Error Detection and<br>Recovery in Multicore<br>Processors | EXHIBITION<br>OPENS AT 1000                                                   |  |  |

|      | Room – Oisans                                                                                                                                      | Room – Meije                                                       | Room – Belle-Etoile                                                      | Room - Stendhal                                                | Room – Chartreuse                                                                   | Room – Bayard                                                               | Room – Les Bans                                                                                                      | Exhibition Theatre                                                            |  |  |

| to   | 6.1.1<br>SMART DEVICES HOT<br>TOPIC/EMBEDDED TUTORIAL<br>– Ultra Low Power Smart<br>Devices                                                        | 6.2<br>Placement and<br>Floorplanning                              | 6.3<br>Power Modelling, Analysis<br>and Optimisation                     | 6.4<br>Design and Test of Fault<br>Resilient NoC Architectures | 6.5<br>New Techniques for<br>Diagnosis and Debug                                    | 6.6<br>Embedded Software for<br>Parallel Architectures                      | 6.7<br>HOT TOPIC - Virtual<br>Manycore Platforms:<br>Moving Towards 100+<br>Processor Cores                          | 6.8<br>PANEL SESSION –<br>Embedded Software Debug<br>and Test                 |  |  |

| 1340 | 6.1.2 SPECIAL DA                                                                                                                                   | Y KEYNOTE AND AWARDS                                               | 1340-1400 Awards and 14                                                  | 00-1430 Keynote, Room –                                        | Oisans                                                                              |                                                                             |                                                                                                                      |                                                                               |  |  |

|      | Room – Oisans                                                                                                                                      | Room – Meije                                                       | Room – Belle-Etoile                                                      | Room – Stendhal                                                | Room – Chartreuse                                                                   | Room – Bayard                                                               | Room – Les Bans                                                                                                      | Exhibition Theatre                                                            |  |  |

|      | 7.1<br>SMART DEVICES HOT TOPIC<br>– Smart Medical Implants                                                                                         | 7.2<br>Emerging Memory<br>Technologies                             | 7.3<br>Architectural Optimisation<br>for Low Power Systems               | 7.4<br>Advanced Technologies for<br>NoC Implementation         | 7.5<br>Emerging Test Solutions for<br>Advanced Technologies, RF<br>and MEMS Devices | 7.6<br>Innovative Power-Aware<br>Systems for a Green and<br>Healthy Society | 7.7<br>HOT TOPIC – Foundations of<br>Component-Based Design<br>for Embedded Systems                                  | 7.8 EMBEDDED TUTORIAL – Predictable System Integration                        |  |  |

|      | Room – Oisans                                                                                                                                      | Room – Meije                                                       | Room – Belle-Etoile                                                      | Room – Stendhal                                                | Room – Chartreuse                                                                   | Room – Bayard                                                               | Room – Les Bans                                                                                                      | Exhibition Theatre                                                            |  |  |

| to   | 8.1<br>SMART DEVICES PANEL<br>SESSION — Integrating the<br>Real World Interfaces                                                                   | 8.2<br>System-Level Design<br>Techniques for Automotive<br>Systems | 8.3<br>Power/Error Tradeoffs                                             | 8.4<br>Memory System<br>Architectures                          | 8.5<br>Testing and Designing<br>SRAM Memories                                       | 8.6<br>Cryptanalysis, Attacks and<br>Countermeasures                        | 8.7<br>HOT TOPIC – Flows,<br>Application and Future of<br>Component-based Design<br>for Embedded Systems             | 8.8 EMBEDDED TUTORIAL – Communication Networks in Next Generation Automobiles |  |  |

|      | * • ·                                                                                                                                              | T#IIIRS                                                            | ΠΔΥ •                                                                    | THIIR                                                          | SDAY •                                                                              | THIIR                                                                       | thursday 1                                                                                                           | .7 march                                                                      |  |  |

|                    | *                                                                                                             |                                                                                 | DAY                                                                               | THUK.                                                            | DUAL                                                           | ' INUK                                                                   | tiluisuay 1                                                                                                                | .7 march                                                                                   |

|--------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 0730               | REGISTRATION & S                                                                                              | SPEAKERS' BREAKFAS                                                              | BREAKS 1000-                                                                      | 1100 Exhibition Break                                            | (1000-1030 IP4), 1230-                                         | 1330 Lunch, 1530-1600                                                    | Break (1530-1600 IP5)                                                                                                      |                                                                                            |

|                    | SPECIAL TRACK                                                                                                 | EMERGING TECHNOLOGIES                                                           | APPLICATIONS                                                                      | DESIGN TECHNOLOGY                                                | TEST                                                           | EMBEDDED SOFTWARE                                                        | SYSTEM DESIGN                                                                                                              | SPECIAL SESSIONS                                                                           |

|                    | Room - Oisans                                                                                                 | Room – Meije                                                                    | Room – Belle-Etoile                                                               | Room - Stendhal                                                  | Room – Chartreuse                                              | Room - Bayard                                                            | Room – Les Bans                                                                                                            | Exhibition Theatre                                                                         |

| 0830<br>to<br>1000 | 9.1 INTELLIGENT ENERGY<br>MANAGEMENT TUTORIAL –<br>Energy Transfer, Generation<br>and Power Electronics       | 9.2<br>Design Automation<br>Methodologies for Emerging<br>Technologies          | 9.3<br>System Modelling                                                           | 9.4<br>Modelling and Verification<br>of Analogue and RF Circuits | 9.5<br>INDUSTRIAL 2                                            | 9.6<br>Embedded System Resource<br>Allocation and Management             | 9.7<br>EMBEDDED TUTORIAL –<br>Sub-Wave Length<br>Lithography and Variability<br>Aware Test and<br>Characterisation Methods | EXHIBITION<br>OPENS AT 1000                                                                |

|                    | Room - Oisans                                                                                                 | Room – Meije                                                                    | Room – Belle-Etoile                                                               | Room – Stendhal                                                  | Room – Chartreuse                                              | Room - Bayard                                                            | Room – Les Bans                                                                                                            | Exhibition Theatre                                                                         |

| 1100<br>to<br>1230 | 10.1.1 INTELLIGENT ENERGY MANAGEMENT – Smart Energy Generation: Design Automation and the Smart-Grid          | 10.2<br>Advanced Algorithms and<br>Applications for<br>Reconfigurable Computing | 10.3<br>System Optimisations and<br>Adaptivity                                    | 10.4<br>Design and Simulation of<br>Mixed-Signal Systems         | 10.5<br>Advances in Test<br>Generation and Fault<br>Simulation | 10.6<br>Model Based Verification<br>and Synthesis of Embedded<br>Systems | 10.7<br>EMBEDDED TUTORIAL — Die<br>Stacking Goes Mobile and<br>Embedded                                                    | 10.8<br>PANEL SESSION -State of<br>the Art Verification<br>Methodologies in 2015           |

| 1330               | 10.1.2 SPECIAL                                                                                                | DAY KEYNOTE, 1330-1400                                                          | Keynote, Room – Oisans                                                            |                                                                  |                                                                |                                                                          |                                                                                                                            |                                                                                            |

|                    | Room - Oisans                                                                                                 | Room – Meije                                                                    | Room - Belle-Etoile                                                               | Room - Stendhal                                                  | Room – Chartreuse                                              | Room – Bayard                                                            | Room – Les Bans                                                                                                            | Exhibition Theatre                                                                         |

| 1400<br>to<br>1530 | 11.1 INTELLIGENT ENERGY<br>MANAGEMENT – Smart<br>Energy Utilisation: From<br>Circuits to Consumer<br>Products | 11.2<br>Architectural Innovations<br>for Reconfigurable<br>Computing            | 11.3<br>Asynchronous Circuits and<br>Advanced Timing Issues in<br>Logic Synthesis | 11.4<br>High Level Synthesis                                     | 11.5<br>New Directions in Testing                              | 11.6<br>Hardware Design for<br>Multimedia Applications                   | 11.7<br>HOT TOPIC – New Frontiers<br>in Embedded Systems<br>Design: Technology and<br>Applications                         | 11.8<br>HOT TOPIC – Stochastic<br>Circuit Reliability Analysis<br>in Nanometer CMOS        |

|                    | Room - Oisans                                                                                                 | Room – Meije                                                                    | Room – Belle-Etoile                                                               | Room - Stendhal                                                  | Room – Chartreuse                                              | Room - Bayard                                                            | Room – Les Bans                                                                                                            | Exhibition Theatre                                                                         |

| 1600<br>to<br>1730 | 12.1 INTELLIGENT ENERGY MANAGEMENT PANEL SESSION – The Role of the EDA Community                              | 12.2<br>Design and Run-Time<br>Support for Dynamic<br>Reconfigurability         | 12.3<br>Reliability and Error<br>Tolerance in Logic<br>Synthesis                  | 12.4<br>Reliability and Error<br>Tolerance in Logic<br>Synthesis | 12.5<br>Error Correction and<br>Resilience                     | 12.6<br>Security Modules from<br>Layout to Network-on-Chip               | 12.7<br>HOT TOPIC – Sustainability<br>through Massively<br>Integrated Computing                                            | 12.8<br>HOT TOPIC – Synthesis<br>Supported Increase of<br>Efficiency in Analogue<br>Design |

## monday 14 march

| REAKS              | 1100-1130 Morning 1300-1                                                                  | 1430 Lunch, 1600-1630 Afterno                                    | on                                                                                 |                                                                  |

|--------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------|

| NEARS              | 1100-1130 Worlding, 1300-                                                                 | 1430 Lulicii, 1000-1030 Aiteilio                                 | uli.                                                                               |                                                                  |

|                    | A (Room - Belle-Etoile)                                                                   | B (Room – Chartreuse)                                            | C (Room – Les Bans)                                                                |                                                                  |

| 1930<br>to<br>1800 | Low Power SOC Design: Best Practice<br>– and what's next?                                 | Electronic System Level Design and<br>Verification               | Manufacturing, CAD and Thermal-<br>Aware Design for 3D System-on-Chip<br>Design    |                                                                  |

|                    | D1 (Room - Meije 3)                                                                       | E1 (Room – 7 Laux 4)                                             | F1 (Room – 7 Laux 5)                                                               | G1 (Room – Room Meije 2)                                         |

| 1300               | MPSoC Hardware/Software<br>Architectural and Design<br>Challenges/Solutions               | On-chip interconnect for new generation of SoC                   | Renewable energy: solar power generation, conversion and delivery                  | Power-Aware Testing and Test<br>Strategies for Low Power Devices |

|                    | D2 (Room – Meije 3)                                                                       | E2 (Room – 7 Laux 4)                                             | F2 (Room – 7 Laux 5)                                                               | G2 (Room – Meije 2)                                              |

| to<br>800          | Model-based MPSoC Architecture<br>Synthesis for Highly-demanding<br>Embedded Applications | Design and Verification Challenges<br>for Automotive Electronics | Overcoming CMOS Reliability<br>Challenges: From Devices to Circuits<br>and Systems | Testing TSV-Based 3D Stacked Ics                                 |

plenary session

Tuesday, March 15, 2011, 0830 - 1030 • Opening Address - Awards - Keynote Speakers

# first keynote address

# Biologically-inspired massively-parallel architectures – computing beyond a million processors

S Furber, ICL Professor of Computer Engineering, School of Computer Science, Manchester U, UK

Moore's Law continues to deliver ever-more transistors on an integrated circuit, but discontinuities in the progress of technology mean that the future isn't simply an extrapolation of the past. For example, design cost and complexity constraints have recently caused the microprocessor industry to switch to multi-core architectures, even though these parallel machines present programming challenges that are far from solved. Moore's Law now translates into ever-more processors on a multi-, and soon many-core chip. The software challenge is compounded by the need for increasing fault-tolerance as near-atomic-scale variability and robustness problems bite harder.

We look beyond this transitional phase to a future where the availability of processor resource is effectively unlimited and computations must be optimised for energy usage rather than load balancing, and we look to biology for examples of how such systems might work. Conventional concerns such as synchronisation and determinism are abandoned in favour of real-time operation and adapting around component failure with minimal loss of system efficacy.

# second keynote address

# How technology R&D leadership brings a competitive advantage in the fields of multimedia convergence and power applications

Philippe Magarshack, Group Vice-President, Technology R&D - General Manager, Central CAD and Design Solutions, STMicroelectronics, France

From 1985 to 1989, Magarshack designed microprocessors arithmetic blocks at AT&T Bell Labs in New Jersey, Pennsylvania and California. In 1989, he joined Thomson-CSF in Grenoble, France, as libraries and ASIC Manager. In 1994, Magarshack joined the Central R&D of SGS-THOMSON Microelectronics (now STMicroelectronics), where he held several Program Management roles in advanced CMOS Design Platforms. Since 2005, Magarshack heads ST's Central Library, IP and CAD organisation, which defines and provides design solutions to all ST Product Groups in CMOS, embedded NVM and BCD processes, ranging from 0.35um to

20nm technologies.

In his current role, Magarshack oversees ST's EDA vendor strategy, setting up and managing joint R&D programs to address ST's future design needs. Magarshack is ST's Enablement Executive at the IBM ISDA CMOS Bulk Alliance in 32/28nm and 22/20nm.

Philippe Magarshack was born in London, UK, and graduated with an engineering degree in Physics from Ecole Polytechnique in Palaiseau, France in 1983 and with an Electronics Engineering degree from Ecole Nationale Supérieure des Télécommunications in Paris, France in 1985.

# WIRELESS NETWORK for LAPTOP USERS

Access will be FREE throughout the exhibition area for all attendees

# LUNCH AND LEARN SESSION SPONSORED BY MENTOR GRAPHICS -

Grenoble EDA Ecosystem -From Research to Market -Time: 1300 - 1400

Location / Auditorium Dauphine

Moderator: Mark Croft, Mentor Graphics, UK

Three views of the value of European Research to EDA and Semiconductors: CEA-LETI, ST and Mentor Graphics speak of the value of close cooperation in the EU.

# 1300 FROM RESEARCH TO MARKET Laurent Malier, CEO, CEA-LETI, FR

With its research centers, university campus, 500 foreign companies and 40,000 scientists, engineers and technicians employed in the area, the Grenoble-Isere region, otherwise known as France's Silicon Valley, mixes world-class intellectual and scientific dynamism with exceptional quality of life. It is the ideal sprinboard for Academia-Industry collaboration. This presentation details collaboration schemes between Industry and research institutes and industry happening in Grenoble. This often involves long-term projects based on sharing research costs and requires joint technical programs with a predeterminable timetable, with specific technology transfer and operating conditions.

# 1320 SUCCESSFUL R&D COLLABORATIONS AS A COMPETITIVE ADVANTAGE

Philippe Magarshack, Group Vice-President, Technology R&D - General Manager, Central CAD and Design Solutions, STMicroelectronics, FR

STs Grenoble center was born as a spin-off from a Grenoble research lab several decades ago. Since then we have continued to maintain our innovation leadership with long-term Public-Private Partnerships in Grenoble, France and Europe. Starting in 1992, ST has partnered with its competitors to build its 200mm and 300 mm R&D centers and fabs in Crolles, near Grenoble. In 2008, ST joined ISDA alliance in Fishkill NY to collaborate to its 32/28mm and 20nm CMOS processes. More recently, ST has reinforced and enlarged the scope of its local R&D partnership to Design and Design Automation. This complete ecosystem is now bringing valuable innovation to our products and our customers.

# 1340 INVESTING IN THE TOP TALENT FOR EDA

#### Eric Selosse, Vice President and General Manager, Emulation Division, Mentor Graphics, FR

Mentor Graphics has a long track record of investing in Europe for R&D expertise. Over the last year, despite the economic conditions, we have continued to recruit in France, the UK and Poland. Our industry is a meritocracy which relies on the hiring, nurturing and retention of the best world-class engineers available in electronics and associated fields. This presentation will outline why we invest in Europe, why France is such a significant part of this and look at the particular place Grenoble has in this story.

# Smart Devices of the Future Special Day

EMBEDDED TUTORIAL – Smart Devices for the Cloud Era

Room - Oisans 0830-1000

Organisers/Moderators: A Jerraya, CEA-LETI MINATEC, FR

J Goodacre, ARM, UK

Cloud computing will provide unlimited computing power and mobile terminals will take benefit of these new flexible computing platforms. This session presents the context of future mobile terminals, the key evolutions that will enable access to cloud computing and the new functions that will require cloud computing.

HOT TOPIC/EMBEDDED TUTORIAL – Ultra Low Power Smart Devices

Room - Oisans 1100-1230

Organisers/Moderators: J Goodacre, ARM, UK

A Jerraya, CEA-LETI MINATEC, FR

Low power is considered the key enabling technology for future smart systems. For most applications stringent requirements on power consumption has to be satisfied. This session presents power issues in different application domains and how specific requirements are addressed. This is illustrated with hardware/software design techniques for concrete products.

HOT TOPIC – Smart Medical Implants

Room - Oisans 1430-1600

Organisers:

A Jerraya, CEA-LETI MINATEC, FR

J Goodacre, ARM, UK

Moderator:

S Yoo, POSTECH, KR

Medical implants integrate a large number of heterogeneous components (computing, sensors, actuators, antenna, RF) to implement sophisticated functions. Unlike classic devices, the design of medical implants includes the building of application specific architecture and specific interfaces and other kinds of packaging required to efficiently interface with human body. This session introduces the key technologies for the design of such complex devices.

PANEL SESSION – Integrating the Real World Interfaces

Room - Oisans

1700-1830

Organisers/Moderators:

A Jerraya, CEA-LETI MINATEC, FR

J Goodacre, ARM, UK

Panellists:

P Urard, STMicroelectronics, FR

J Rabaey, UC Berkeley, US

R Bramley, STEricsson, FR A King-Smith, IMGTEC, UK

W Burleson, Massachusetts U, US

F Perruchot, CEA-LETI, FR

Smart systems require interfacing more of the world in an integrated solution (Camera, gyroscope, compass, temp, direction...). This is imposed by social evolution and enabled by new integration technologies. So far, many products featuring a variety of hardware and software have been developed and many more seems to be coming in a fast growing market. The panel will present the most promising products and solutions and discuss the innovations enabling future smart systems.

#### LUNCH-TIME KEYNOTE AND AWARDS

Room – Oisans - 1340-1400 Awards and 1400-1430 Keynote

1340

Awards Moderator: Z Peng, Linkoping U, SE

Awards: Presentation of the DATE 10 Best Paper Awards:

TRACK D - PROPERTIES OF AND IMPROVEMENTS TO TIME-DOMAIN DYNAMIC THERMAL ANALYSIS ALGORITHMS X Chen and R P Dick, U of Michigan, US L Shang, U of Colorado at Boulder, US

TRACK E - SKEWED PIPELINING FOR PARALLEL SIMULINK SIMULATIONS

A Canedo, T Yoshizawa and H Komatsu, IBM Research, JP

BEST IP - TOWARDS A CHIP LEVEL RELIABILITY SIMULATOR FOR COPPER/LOW-K BACKEND PROCESSES

M Bashir and L Milor, Georgia Institute of Technology, US

Presentation of the EDAA Outstanding Dissertation Awards 1400

Organiser/Moderator: A Jerraya, CEA-LETI MINATEC, FR

Keynote Speaker:

**Hannu Kauppinen,** Director, Head of Radio Systems Laboratory, Nokia Research Center, FI

#### WIRELESS INNOVATIONS FOR SMARTPHONES

Abstract: The ever increasing demand for fast mobile internet connectivity continues to set challenges for research in radio communications. On one hand the capacity demand can be served by offloading data traffic to local networks. On the other hand using more bandwidth, and possibly dynamically allocating spectrum in a flexible way, will improve the usage of the available spectrum. The future of wireless access continues to be defined by the 3GPP and IEEE standards setting bodies. Radios can also provide innovative features that offer new functionalities for consumers, such as ultra fast local connectivity, sensing and positioning.

## thursday 17 march

# Intelligent Energy Management - Supply and Utilisation Special Day

**Energy Transfer, Generation** and Power Electronics

Room - Oisans 0830-1000

Organisers:

P Mitcheson, Imperial College, UK

P K Wright, UC Berkeley, US

Moderator

P Mitcheson, Imperial College, UK

Issues relating to energy resources are set to play an increasing role in all of our futures. This special day at DATE is intended to further involve the EDA community in energy related matters at all scales. This session covers setting the scene for the day on energy, covering topics from levels of micro Watts to Giga Watts.

Smart Energy Generation: Design Automation and the Smart-Grid

Room - 0isans 1100-1230

Organisers:

P Mitcheson, Imperial College, UK

P K Wright, UC Berkeley, US

Moderator:

P K Wright, UC Berkeley, US

This session will look at issues relating to the supply side of the electrical grid, including smart grids and the role of electric vehicles in future supply infrastructure and includes talks from both industry and academia.

Smart Energy Utilisation: From Circuits to Consumer Products

Room - Oisans 1400-1530

Organisers:

P Mitcheson, Imperial College, UK

P K Wright, UC Berkeley, US

Moderator:

P Mitcheson, Imperial College, UK

This session concentrates on smart use of energy at the demand side - from energy issues at the circuit level to larger scale issues with consumer products and use of energy in the home.

\*12.1 \*

The Role of the EDA Community in the Future of World Energy Supply and Conservation?

Room - 0isans 1600-1730

Organisers/Moderators:

P K Wright, UC Berkeley, US P Mitcheson, Imperial College, UK

Panellists:

**L Bomhold,** Synopsys, US

T Green, Imperial College, UK

A Ephrimides, Maryland U, US

pricing requires new technologies.

C Blumstein, California Institute for Energy and Environment IIS

S Henry, RTE, FR

Until recently the electrical power industry has relied solely on traditional technologies - copper and iron as cables, transformers and machines as the mainstream solution for the generation, transmission and distribution of power. Whilst use of these materials and technologies is here to stay, improvements in power semiconductor technology mean that the industry is moving into a position where more and faster control of power systems can be achieved. This high level control requires a sensing and communication infrastructure to be put in place across the network. At the same time, the use of electricity in the home, through the potential of real time consumer

This panel session aims to pull together heavy current electrical power engineers and light current electronic engineers to form a discussion and debate about the future role of EDA in applications which are being brought about by changes in the functioning of the power industry. Power engineers from both industry and academia will stimulate the discussion with requirements both from a system perspective and consumer perspective. The representatives from the EDA side will respond with what contributions they believe EDA can make, what already exists or is a simple development problem and what research issues remain in achieving these goals. In summary, this panel aims to provide motivation for the EDA industry to work on useful technology that can be applied to heavy power systems with a view to improving global energy efficiency.

SPECIAL DAY KEYNOTE

thursday**≁**17 march

Room - 0isans 1330-1400

Organiser:

P K Wright, UC Berkeley, US

Keynote Speaker:

Carmelo Papa, Executive VP Industrial and Multisegment, STMicroelectronics, IT

#### **SMART ENERGY AT ST**

The exponential increase of world energy demand, with a forecasted raise of 45%[1] between 2010 and 2030, makes energy management one of the most urgent topics of the century and a key driver for semiconductors and electronics products evolution. The main solutions for world energy demand and global warming issues have been individuated in two main streams: an increasing offer from alternative energy sources and their integration into the new Smart Grid and a reduction of the demand through an increase of systems efficiency.

In energy supply and distribution, the Smart Grid is in fact impacting for an estimated 14% of CO2[2] emissions reduction in the global energy system by 2020. In addition it makes it possible to generate high cost savings for industrial and economic system (188 Billion\$ per year estimated only for U.S.[2])

New measures for Energy Efficiency will contribute up to 8 Giga-Tons of CO2 reduction (54% of total with the application of policy 450[1]) by 2020, mostly thanks to power electronics applications.

Along these two areas of intervention, ST is investing to provide both effective power semiconductor technologies and ICs for new topologies for power conversion, but not only. New materials (SiC) for power transistors, innovative solutions for power management and digital control, wired and wireless ICs are some examples of ST offer that apply to energy related applications like PV converters, Smart Metering, Connectivity, Building Automation, Electrical Traction and Motor Control.

Along the energy theme, though at different orders of magnitude, innovation for portable systems is tackled at ST R&D: extremely low consuming CMOS technology for digital ICs, low power RF transceivers, milliWatt capable super thin batteries and 3D integration techniques are the base for miniaturised, long lasting battery based systems, that enable new scenarios especially in portable Healthcare and Wireless Autonomous Sensors Networks.

- [1] Source: International Energy Agency

- [2] Source: The Climate Group

- [3] Source: Grid 2030 A National Vision for Electricity's Second 100 Years, United States Department of Energy, Office of Electric Transmission and Distribution

# **Friday Workshops**

0730 WORKSHOP REGISTRATION & WELCOME REFRESHMENTS

BREAKS Please see individual workshop programmes for lunch and break times

|                    | Room – Les Bans                                                                 | Room – Meije                                                                          | Room – Bayard                                                                                                                           | Room – Berlioz                                                                           |

|--------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 0830<br>TO<br>1700 | W1 Workshop on Micro Power<br>Management for Macro Systems on<br>Chip (uPM2SoC) | W2 Design Methods and Tools for<br>FPGA-Based Acceleration of<br>Scientific Computing | W3 Third Friday Workshop on<br>Designing for Embedded Parallel<br>Computing Platforms: Architectures,<br>Design Tools, and Applications | W4 Bringing Theory to Practice:<br>Predictability and Performance in<br>Embedded Systems |

|                    |                                                                                 |                                                                                       |                                                                                                                                         |                                                                                          |

|                    | Doom Standbal                                                                   | Boom 7 Laury 6                                                                        | Doom Pollo Stoilo                                                                                                                       | Boom Chartrouse                                                                          |

| koom – Stendnat | Room – / Laux 4                                                                              | Room - Belle-Etoile                                        | Room - Chartreuse                              |

|-----------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------|

|                 | W6 M-BED'2011, the 2nd Workshop<br>on Model Based Engineering for<br>Embedded Systems Design | W7 Hardware Dependent Software<br>Solutions for SoC Design | W8 1st International QEMU Users<br>Forum (QUF) |

|                 |                                                                                              |                                                            |                                                |

# DATE 11 OPENING PLENARY

## **Auditorium Dauphine**

Biologically-inspired massively-parallel architectures – computing beyond a million processors

S Furber, ICL Professor of Computer Engineering, School of Computer Science, Manchester U, UK

How technology R&D leadership brings a competitive advantage in the fields of multimedia convergence and power applications

P Magarshack, Group Vice-President, Technology R&D - General Manager, Central CAD and Design Solutions, STMicroelectronics, FR

See you at DATE 12, 12-16 March 2012, ICC, Dresden, Germany

#### exhibition theatre

# tuesday 15 march

#### ETO1 Highlights of DATE11 Exhibition /Clustering – an Enabler for Micro and **Nanoelectronics**

1045 - 1115

Organiser/Moderator:

Juergen Haase, edacentrum, Germany

Speaker:

Andreas Bruening, Silicon Saxony, Germany

Abstract: Each morning Juergen Haase (edacentrum, Germany) will open DATE11 Exhibition with an overview about the highlights of the Exhibition program and provide brand-new information on "What's hot today" to all attendees

Andreas Brüning, in the Silicon Saxony Cluster (Germany) responsible for the work of the micro/nanoelectronic devision, will invite all attendees to establish close collaboration between clusters like Grenoble and Dresden

Clustering: an Enabler for Micro and Nanoelectronics A short overview about Silicon Saxony will be followed by describing micro and nanoelectronics as an opportunity for Europe as well as clustering as an enabler for micro and nanoelectronics based on the example Grenoble and Dresden. Presentation of Dresden & Genoble cluster as a cooperation for Europe and the expectation to strengthen exchange in Design Automation experience.

#### 2.8 EMBEDDED TUTORIAL -**Addressing Critical Power** Management Verification Issues in **Low Power Designs**

1130 - 1300

Organiser:

B Kapoor, Mimasic, US

Moderator: K Just, Infineon, DE

Abstract: Power management techniques that leverage voltage as a handle are being extensively used in power sensitive designs. These techniques include power gating. power gating with retention, multiple supply voltages, dynamic voltage scaling, adaptive voltage scaling, multi-threshold CMOS, and active body bias. The use of the power management techniques also imply new challenges in validation and testing of designs as new power states are created. We look into verification issues along with the solutions to these issues using a verification strategy that involves power-aware simulation, rule-based structural checking, formal tools, and methodology recommendations. We detail our varied experiences with various design teams in addressing these low power verification issues for applications such as the wireless handset, low power microprocessors, and GPS.

#### 3.8 PANEL SESSION - Power Formats: **Beyond UPF and CPF**

1430 - 1600

Organiser/ Moderator: B Pangrle, Mentor Graphics, US

Panellists:

J Biggs, ARM, UK

C Clavel, ST-Ericsson, FR

O Domerego, Texas Instruments, FR

K Just, Infineon/Intel, DE

B Moison, STMicroelectronics, FR

Abstract: Two formats for specifying power intent are currently in wide use in industry today and as designers continue to strive for more power efficient designs new issues arise that certainly need new solutions to improve on today's standards. This panel will discuss areas for improving today's power formats and the direction that these formats need to move in order to provide the most efficient flows for design and verification and especially with regards to low-power. The scope of the formats and their suitability from early ESL design exploration to backend sign-off checking will also be discussed along with any issues that need to be addressed in order to make design and verification engineers more productive.

#### ETO2 What is missing to enable global IP collection, assembly, and virtual platform distribution?

1615 - 1715

Organiser: Magillem

Moderator:

Mladen Berekovic, University of Jena, Germany

Speakers/Panellists:

Cyril Spasevski, Magillem, CTO, France

Michael McNamara, Cadence, VP and GM and System Software Group, USA

John Goodenough,

ARM, VP Design Technology and Automation, UK

Antoine Perrin, ST, CAD Manager, France

Abstract: The domains of RTL design, virtual platforms, high level synthesis, and IP assembly automation are converging to enhance the productivity and reliability of system level design methodology. A significant number of companies are creating RTL IP catalogs and leveraging assembly automation to rapidly produce incrementally innovative SoCs. Virtual platforms are enabling a growing practice pre-RTL software development. High level synthesis is increasing the productivity to create new RTL IP. The confluence of these forces is creating a plethora of opportunities, and presenting several challenges. This panel will explore and debate the priorities and benefits of these emerging trends and discuss the following questions:

- How far along are customers in creating internal virtual platform IP catalogs?

- What are the challenges of organizing virtual platform and RTL IP catalogs?

- How do IP-XACT and assembly tools help with this internal management problem

- Are companies starting to organize 3rd party IP suppliers to provide virtual platform and RTL IP, as well as IP-XACT

- What are the challenges in defining IP catalog requirements to 3rd parties?

- Are standards needed in addition to IP-XACT to enable freer IP creation and exchange?

#### **ETO3 STMicroelectronics automates** quality monitoring for improved design productivity

1730 - 1750

Organiser:

Satin Technologies, STMicroelectronics

Speaker:

Indavong Vongsavady, ST CCDS

Abstract: The Central CAD and Design Solutions (CCDS) group at STMicroelectronics is in charge of developing and deploying design libraries, kits, flows and methodologies throughout the different groups at ST and ST-Ericsson. They also offer internal design services for very complex chips.

In order to make design quality monitoring more timely and accurate, ST CCDS has adopted VIP Lane to help turning their design checklists into fully automated dashboards. These dashboards are becoming the foundation for on-the-fly, fact-based communication between all stakeholders of the same design project. This presentation will show the benefits of this approach

(sharing of more formal design practices, accurate communication between design teams, shorter design cycle) and illustrate these benefits with real life examples.

#### **ET04 Optimization of Power-MOS** Structures dedicated to Energy **Management ICs**

1750 - 1810

Organiser:

Edxact, ST-Ericsson

Speaker:

Jérôme Lescot, ST-Ericsson, France

Abstract: Impact of metal routing on 'rdson' parameter of power-MOS devices is increasing with more advanced process nodes (65n, 40n). Capacity of comanche tool to quickly extract thousands of pin to pin resistances enables us to achieve layout optimization by analysing resistances distribution from pads to any individual transistor. In addition, jivaro reduction makes possible the spice simulation of the structure including both parasitic resistors and functional devices to extract rdson parameter.

#### **Exhibition Theatre Overview**

|             | Tuesday 15th March                                                                                                | V           | Vednesday 16th March                                                                                              |             | Thursday 17th March                                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------|

| 1045 - 1115 | <b>ETO1 Day 1 Opening Session:</b> Highlights of Date11 Exhibition / Clustering – An Enabler for                  | 1000 - 1030 | ETO6 Day 2 Opening Session: Highlights of<br>Date11 Exhibition / More Than Moore Solutions                        | 1000 - 1010 | <b>ETO9 Day 3 Opening Session:</b> Highlights of Date11 Exhibition / Testimonials                                       |

| 1130 - 1300 | Micro and Nanoelectronics  2.8 Embedded Tutorial: Addressing Critical Power Management Verification Issues in Low | 1030 - 1050 | for Automotive Products  ETO7 Testimonial: Ball Grid Array Packages  Electrical Optimization Using Apache Package | 1010 - 1030 | <b>ET10 Testimonial:</b> System Level Power<br>Integrity Analysis and Supply Network<br>Optimization of a Dual Core CPU |

| 1430 - 1600 | Power Designs  3.8 Panel: Power Formats: Beyond UPF and CPF                                                       | 1100 - 1230 | Modeling Tools <b>6.8 Panel:</b> Embedded Software Debug and Test                                                 | 1030 - 1050 | ET11 Testimonial: Co-Verification of an<br>Interrupt Driven Firmware Subsystem using                                    |

| 1615 - 1715 | ETO2 Panel: What is Missing to Enable Global                                                                      | 1315 - 1415 | ETO8 Panel: Process Variability: Challenges and                                                                   |             | Cadence ISX and Coverage Driven Techniques                                                                              |

|             | IP Collection, Assembly, and Virtual Platform<br>Distribution?                                                    | 1430 - 1600 | Solutions 7.8 Embedded Tutorial: Predictable System                                                               | 1100 - 1230 | <b>10.8 Panel:</b> State of the Art Verification Methodologies in 2015                                                  |

| 1730 - 1830 | ETO3 Testimonial: STMicroelectronics                                                                              | 3.00 3.00   | Integration                                                                                                       | 1245 - 1345 | ET12 Panel: Early Timing and Power                                                                                      |

|             | Automates Quality Monitoring for Improved<br>Design Productivity                                                  | 1700 - 1830 | <b>8.8 Embedded Tutorial:</b> Communication Networks in Next Generation Automobiles                               |             | Information of Complex SoC Designs using<br>Augmented Virtual Platforms                                                 |

|             | <b>ETO4 Testimonial:</b> Optimization of Power-Mos<br>Structures Dedicated to Energy Management ICS               |             |                                                                                                                   | 1400 - 1530 | <b>11.8 Hot Topic:</b> Stochastic Circuit Reliability Analysis in Nanometer CMOS                                        |

|             | ETO5 Testimonial: How Software Development                                                                        |             |                                                                                                                   | 1700 - 1830 | <b>12.8 Hot Topic:</b> Synthesis Supported Increase of the Analog Design Efficiency                                     |

# exhibition theatre

#### ET05 How Software development can take benefit of a platform power model

1810 - 1830

Organiser: DOCEA Power, ST-Ericsson

Speaker:

Patrick Arnould, Senior System Architect,

ST-Ericsson, France

Abstract: The increasing complexity of applications running on multimedia mobile platforms is becoming more and more critical for battery life, so software optimization to take into account power consumption is crucial but could become very painful without a dedicated environment. A lot of power saving is possible at the software level but the investigations are complex due to the number of parameters involved in this optimization: clock gating, dynamic power switching, dynamic voltage and frequency scaling, traffic, CPU and IP load.

In this testimonial, a validation environment will be used as an example to show the benefit for software developers to have access to a combination of CPU load, traffic and power figures phase per phase and power supply per power supply. It also outlines the challenges for a power modeling methodology to be able to target a wide range of applications, very low power and power hungry systems optimization. Taking the benefit of having a platform power model and before starting any software development, key decisions can be taken to focus very quickly on the best software option to gain power.

The testimonial scope goes from power model construction to fast software optimization on a real application showing the benefit to speed up software development and platform power optimization.

# wednesday 16 march

#### ETO6 Highlights of DATE11 Exhibition More than Moore Solutions for **Automotive Products**

1000 - 1030

Organiser/Moderator:

Juergen Haase, edacentrum, Germany

Speaker:

Andreas Bruening, ZMD, Germany

Abstract: Each morning Juergen Haase (edacentrum, Germany) will open DATE11 Exhibition with an overview about the highlights of the Exhibition program and provide brand-new information on "What's hot today" to all attendees.

Andreas Brüning, director technology office of ZMD (Germany), will review the productivity in designing More than Moore applications and discuss what is required for analog-mixed signal automotive products in his talk: Trends, Challenges and Solution Statements for More than Moore concerning Analog-Mixed Signal Automotive **Products**

Analog Mixed Signal is a very healthy niche regarding micro-/nanoelectronics. Unfortunately the design productivity has not developed much during the last decade and is far behind the More Moore miniaturization. The talk is dealing with the increasing complexity and related productivity based on an analog-/mixed signal benchmark. Demonstrating design challenges, optimization areas and existing solutions. As a result the hot topics for productivity increase are shown.

#### ETO7 Ball Grid Array Packages electrical optimization using Apache package modeling tools

1030 - 1050

Organiser: Apache / ST

Yvon Imbs, ST Corporate Packaging & Automation, France Laurent Marechal, ST Corporate Packaging & Automation, France

Abstract: Today's packages are facing many challenges linked to cost pressure, Time to Market improvement, miniaturisation. These evolutions are not, for some of them, moving in the right direction to sustain the

performances expected by the end users.

Cost pressure is leading to reduction of area for the Silicon and for the mass production packages will lead to a limitation to off-the-shelf technologies or development of new cost reduction processes and technologies.

Time to market is requesting first design to be the final product. This can only be achieved by an increase effort in term of modelling. Modelling in therefore mandatory in all fields, system level, component level, die level etc... All physical domains are contributing: electrical, thermal, mechanical & thermo-mechanical.

Miniaturisation will request smaller package, thinner traces, thinner substrate. All these aspects have consequences on the electrical behaviour of the package. From a "electrical transparent" media in the end of 1999, there are now becoming the bottlenecks in many applications.

In this talk we will first demonstrate the effects of these constraints on real package designs, in term of application speed, bandwidth of signals, and impact on the margins. We will also explain why the counterpart of this increasing complexity in the package is requesting the help of new tools that can bridge the several part of the system to ensure a full system optimisation.

Preliminary package studies are necessary to define the packaging technology that needs to be optimized versus the die and the board. It consists in impedance computation, interfaces layout strategy and power delivery strategy. The used tools and the results expected from these preliminary studies may differ depending the application and/or the interfaces.

Digital consumer projects (TV, Computer, etc...) are usually using quite big packages as they are not constrained by a form factor. This enables the use of power & ground planes on dedicated layers of the package. The package size and the interface speed are thus requesting a control of the impedance for both single and differential signals. We will show simulation results based mainly on digital projects (TV applications, Computer & Broad band signals). Several modelling tools have been used:

- \* 2D tools (Ansoft) are used to define the impedance guideline derived from the selected technology

- \* Fast quasi-static modelling tools enables the extraction of the preliminary design databases models for both signal nets and power delivery network

First order results will then permit to validate some early choices in term of technology and routing strategy. They are also used to start some preliminary simulation at system level to ensure time to market objectives

More accurate models will generated later on during the design phase to refine the simulations and get more quantitative results (Apache Sentinel PSI, Ansoft HFSS) Package and board resonances can also be studied once the design database are close to completion. Linking the package and board database leads to resonance frequencies that need to be considered versus the application frequencies.

Mobile platform system using multi-GHz CPU cores are needing a proper methodology to handle the power integrity analysis and supply network. The optimization of the power delivery network (PDN) of a System on Chip (SoC) is becoming more and more complex with the increasing operating frequency of its CPU cores.

The defined methodology is mainly using Apache tool features to generate the needed models and run the required analysis. The capabilities of Apache RedHawk are to extract a power model from a SOC, that can be reused in package centric tools to optimise further the power delivery network at package (and board) level. On the other side the package modelling tool (Apache Sentinel NPE) is able to extracted a model that can be imported in the die voltage drop analysis tool (Apache RedHawk) to evaluate the impact of the package routing.

#### SPEAKERS' BIOGRAPHIES

Yvon Imbs joined STMicroelectronics in 2000 after being graduated as a Ph.D from University of Limoges. He worked for 4 years as responsible of electrical package modeling. He started some activities on IC package co-design inside the Telecom, Peripheral & Automotive Division of ST. Then he joined the Corporate Packaging & Automation team. In addition to the electrical package modeling, he started a Package Design Kit activity linked to the ramp-up of the IC-Package co-design activity. Now he's is charge of the electrical driven co-design aimed to ensure the best tradeoff between cost & performances for the BGA packages.

Laurent Marechal joined STMicroelectronics in 2006 after being graduated as M.S. degree in electrical engineering from Polytech'Lille. He joined the Corporate Packaging & Automation team to develop embedded passive devices. In addition he is now in charge of accurate package modeling using 3D Electromagnetical tools and of the support of the electrical driven co-design activity aimed to ensure the best trade-off during BGA package design in close relation with the product Divisions.

#### 6.8 PANEL SESSION - Embedded **Software Debug and Test**

1100 - 1230

Organiser/Moderator:

M Winterholer, Cadence, DE Panellists:

F Cerisier, EASii-IC, FR

S Davidmann, Imperas, UK

L Ducuosso, STMicroelectronics, FR

J Engblom, Simics Wind River, SE