# advance programme

# Design, Automation & Test in Europe

# www.date\_conference.com

# programme guide

| Welcome                                                                                                                     | 3   |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

| General Information                                                                                                         | 6   |

| KEYNOTE SPEAKERS<br>Steve Furber, Manchester U, UK<br>Philippe Magarshack, STMicroelectronics, FR                           | 4   |

| EXECUTIVE TRACK<br>Discussion Panels for Electronic Design Business Managers                                                | 7   |

| SMART DEVICES OF THE                                                                                                        |     |

| FUTURE DAY<br>KEYNOTE: Hannu Kauppinen, Nokia Research Center, FI                                                           | 8   |

| INTELLIGENT ENERGY                                                                                                          | 9   |

| MANAGEMENT – SUPPLY                                                                                                         |     |

| AND UTILISATION DAY<br>KEYNOTE: Carmelo Papa, STMicroelectronics, IT                                                        |     |

| SPECIAL SESSIONS<br>Hot Topics, Panels, Embedded Tutorials                                                                  | 10  |

| DATE 11 - AT A GLANCE<br>A brief overview of the event                                                                      | 12  |

| MONDAY TUTORIALS<br>Eight half-day tutorials, three full-day tutorials                                                      | 17  |

| TECHNICAL SESSIONS<br>Full listing of DATE technical programme, special sessions                                            | 25  |

| AWARDS<br>DATE Awards Ceremony                                                                                              | 55  |

| FRIDAY WORKSHOPS                                                                                                            | 94  |

| EXHIBITION PROGRAMME<br>Exhibitor list, Special Conference Sessions and Business<br>Presentations in the Exhibition Theatre | 113 |

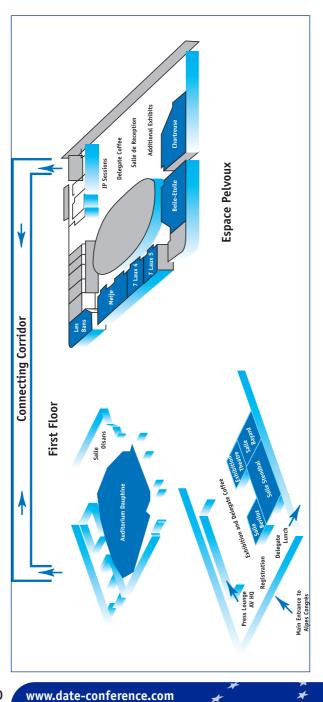

| Detailed Index (inc. Committees and Site Plan)                                                                              | 118 |

www.date-conference.com

×

\*

#### Dear Colleague,

We proudly present to you the Advance Programme of DATE 11. DATE combines the world's favourite electronic systems design conference with an international exhibition for electronic design, automation and test, from system level hardware and software implementation right down to integrated circuit design. While many conferences currently suffer from travel restrictions in many companies and face severe problems in attracting attendees, DATE 2011 received some 950 submissions. The importance of DATE as a worldwide indispensable meeting point is demonstrated by the fact that more than 50% of the submissions came from outside Europe. The most popular topics this year were Simulation/Emulation and Low Power Systems Design, Estimation and Optimisation.

For the 14th successive year DATE has prepared an exciting technical programme, with the help of more

than 300 members of the Technical Programme Committee, who dedicated their time to thoroughly review the submissions, ranging from system level down to circuit design and covering all the most relevant application domains.

This year the conference will be held in France, at Alpexpo in Grenoble and will span an entire working week starting on Monday March 14 with tutorials, and ending on Friday March 18 with workshops.

The plenary keynote speakers on Tuesday are Steve Furber of Manchester University, UK, to talk about 'Biologically-inspired massively-parallel architectures – computing beyond a million processors', and Philippe Magarshack, STMicroelectronics, France to talk about 'How Technology R&D Leadership brings a competitive advantage in the fields of multimedia convergence and power applications'. On the same day, the **Executive Track** offers a series of business panels discussing hot topics in design: 'Ideas on Future of EDA and IP Industry', '22nm Challenges and Wealth/Knowledge Creation Opportunities' and 'System Level Complexity and Innovation'. To emphasise that DATE is the major event for the designers, DATE 11 features invited sessions where **Europe's famous consumer industry presents its best designs and design practices.**

The main conference programme from Tuesday to Thursday includes 77 technical sessions organised in parallel tracks from four areas:

- D Design Methods, Tools, Algorithms and Languages

- A Application Design

- T Test Methods, Tools and Innovative Experiences

- E Embedded Software

Extra tracks are dedicated to the Executive Day on Tuesday and the two special days: **Smart Devices of the Future Day** on Wednesday and **Intelligent Energy Management – Supply and Utilisation Day** on Thursday with Hannu Kauppinen, Nokia Research Center, FI and Carmelo Papa, STMicroelectronics, IT as keynote speakers. Additionally, there are 62 Interactive Presentations which are organised into five IP sessions. Finally, DATE offers a comprehensive overview of commercial design and

verification tools in its exhibition including vendor seminars and abundant networking possibilities with fringe meetings.

We wish you a productive and exciting DATE 11 and a memorable social party on Wednesday evening.

#### DATE 11 General Chair

Bashir Al-Hashimi University of Southampton, UK bmah@ecs.soton.ac.uk

DATE 11 Programme Chair

-

Enrico Macii Politecnico di Torino enrico.macii@polito.it

Tuesday, March 15, 2011, 0830 – 1030 Opening Address – Awards – Keynote Speakers

# Biologically-inspired massively-parallel architectures – computing beyond a million processors

S Furber, ICL Professor of Computer Engineering, School of Computer Science, Manchester U, UK

Moore's Law continues to deliver ever-more transistors on an integrated circuit, but discontinuities in the progress of technology mean that the future isn't simply an extrapolation of the past. For example, design cost and complexity constraints have recently caused the microprocessor industry to switch to multi-core architectures, even though these parallel machines present programming challenges that are far from solved. Moore's Law now translates into ever-more processors on a multi-, and soon many-core chip.

The software challenge is compounded by the need for increasing faulttolerance as near-atomic-scale variability and robustness problems bite harder.

We look beyond this transitional phase to a future where the availability of processor resource is effectively unlimited and computations must be optimised for energy usage rather than load balancing, and we look to biology for examples of how such systems might work. Conventional concerns such as synchronisation and determinism are abandoned in favour of real-time operation and adapting around component failure with minimal loss of system efficacy.

\*

Tuesday, March 15, 2011, 0830 – 1030 Opening Address – Awards – Keynote Speakers

# second keynote address

# How technology R&D leadership brings a competitive advantage in the fields of multimedia convergence and power applications

Philippe Magarshack, Group Vice-President, Technology R&D -General Manager, Central CAD and Design Solutions, STMicroelectronics, France

From 1985 to 1989, Magarshack designed microprocessors arithmetic blocks at AT&T Bell Labs in New Jersey, Pennsylvania and California. In 1989, he joined Thomson-CSF in Grenoble, France, as libraries and ASIC Manager. In 1994, Magarshack joined the Central R&D of SGS-THOMSON Microelectronics (now STMicroelectronics),

where he held several Program Management

roles in advanced CMOS Design Platforms. Since 2005, Magarshack heads ST's Central Library, IP and CAD organisation, which defines and provides design solutions to all ST Product Groups in CMOS, embedded NVM and BCD processes, ranging from 0.35um to 20nm technologies.

In his current role, Magarshack oversees ST's EDA vendor strategy, setting up and managing joint R&D programs to address ST's future design needs. Magarshack is ST's Enablement Executive at the IBM ISDA CMOS Bulk Alliance in 32/28nm and 22/20nm.

Philippe Magarshack was born in London, UK, and graduated with an engineering degree in Physics from Ecole Polytechnique in Palaiseau, France in 1983 and with an Electronics Engineering degree from Ecole Nationale Supérieure des Télécommunications in Paris, France in 1985. general information

This printed programme is intended to provide delegates with an easy reference document during their attendance at DATE 11. Full General Information covering full technical programme details, conference registration costs and booking forms, hotel reservations and booking forms, travel to and in Grenoble, and social event details is available on the conference website - www.date-conference.com

# interactive programme on web

A fully interactive DATE 11 programme is available on the web – **www.date-conference.com** - where you will be able to view the entire detail of the programme and plan your attendance in advance.

-

### venue

The Conference will take place from 14-18 March 2011 and the Exhibition from 15-17 March 2011 in Alpexpo, Avenue d'Innsbruck, Grenoble, France - **www.alpexpo.com**

### date party – wednesday

This year the DATE party will take place in the World Trade Center, Grenoble. The evening will feature a buffet style dinner with plenty of buffet points and drinks to accompany dinner. Musical entertainment with the opportunity to dance will be provided by the popular neo-folk band DJAL. In an enjoyable atmosphere participants will have the opportunity to meet and mingle with their friends and colleagues. All conference attendees, users, vendors and their guests are encouraged to come to the party. Additional tickets for the full Evening Social Programme may be obtained for 70 Euros each (see website for booking forms). Entrance will be by ticket only, so please check that you receive the party ticket when you register.

# cancellation policy

Registered delegates should note that no refunds will be made unless a written request for cancellation is received prior to **18 February 2011.** All refunds are subject to a 10% processing fee. Substitutions will be accepted at any stage.

# interactive presentations

#### Chair: Andrea Acquaviva, Politecnico di Torino, IT

Interactive presentations allow presenters to interactively discuss novel ideas and work in progress that may require additional research work and discussion, with other researchers working in the same area. Interested attendees can walk around freely and talk to any author they want in a vivid face-to-face format. The author may illustrate his work with a slide show on a laptop computer, a demonstration, etc. IP presentations will also be accompanied by a poster. Each IP will additionally be introduced in a relevant regular session prior to the IP Session in a one-minute, one-slide presentation.

To give an overview, there will be one central projection displaying a list of all the presentations going on at the same time in the IP area.

Interactive Sessions will be held in the Salle de Reception area in 30-minute time slots during coffee and exhibition breaks. Coffee and water will be available during the session.

# executive sessions - tuesday

#### Organiser: Yervant Zorian, Synopsys, US

DATE 11 will again feature an Executive Track of presentations by leading company executives (CEOs, Presidents and VPs) representing a range of semiconductor manufacturers, EDA vendors, fabless houses, IP providers and equipments suppliers. This one-day program will be held on Tuesday 15 March, the first day of the DATE conference immediately after the Opening Session and it will be comprised of three sessions where the executives will present their technical/business vision in this nanometer technology era. Each session will feature 5-6 executives and run in parallel to the technical conference tracks. All three executive sessions will first provide each executive with a time-slot to present his/her vision, followed by a question and answer period to provide interaction with the attendees. The Executive Track should offer prospective attendees valuable information about the vision and roadmaps of their corresponding companies from a business and technology point-of-view.

EXECUTIVE SESSION - Ideas on Future of EDA and IP Industry - see page 27

EXECUTIVE SESSION – 22nm Challenges and Wealth/Knowledge Creation Opportunities – see page 34

EXECUTIVE SESSION - System Level Complexity and Innovation - see page 39

#### Organisers:

Ahmed Jerraya, CEA LETI, FR John Goodacre, ARM, US

### Smart Devices of the Future Special Day

Future electronic systems will be dominated by the convergence between design (hardware and software) and fabrication to master next generation smart devices. The design of highly integrated and autonomous intelligent devices for healthcare, mobile and consumer applications require deep knowledge of technology characteristics to reach the required performance. Furthermore, hardware and software are being employed increasingly to overcome fabrication imperfection and to improve yield. This special day will focus on applications, key enabling technologies and future trends driving smart devices of the future.

The **Keynote Presentation** entitled 'Wireless Innovations for Smartphones' will be given by Hannu Kauppinen, Director, Head of Radio Systems Laboratory, Nokia Research Center, Finland.

EMBEDDED TUTORIAL –Smart Devices for the Cloud Era – see page 44

HOT TOPIC/EMBEDDED TUTORIAL – Ultra Low Power Smart Devices – see page 50

SPECIAL DAY KEYNOTE AND AWARDS – see page 55

HOT TOPIC – Smart Medical Implants – see page 56

8

PANEL SESSION – Integrating the Real World Interfaces – see page 62

www.date-conference.com

special day - thursday

Organisers:

Paul Mitcheson, Imperial College, UK Paul K Wright, UC Berkeley, US

# Intelligent Energy Management – Supply and Utilisation Special Day

The links between the disciplines of computation, power electronics, and power systems must become stronger as we move into a world of increasing energy utilisation and efficiency. This special day will foster the necessary links between these separate disciplines through invited presentations from experts in the areas of energy generation, storage and utilisation. The day will also cover recent innovations in enabling technologies for portable devices (energy-

harvesting and wireless powering) and applications of intelligent systems to improve the utilisation of electricity supply through smart metering and infrastructure.

The **Keynote Presentation** entitled 'Smart Energy at ST' will be given by Carmelo Papa, Executive VP Industrial and Multisegment, STMicroelectronics, Italy.

TUTORIAL – Energy Transfer, Generation and Power Electronics – see page 68

Smart Energy Generation: Design Automation and the Smart-Grid – see page 75

SPECIAL DAY KEYNOTE – see page 80

Smart Energy Utilisation: From Circuits to Consumer Products – see page 81

PANEL SESSION – What does the power industry need from the EDA industry and what is the EDA industry doing about it? – see page 88 ×

Special Sessions Chairs: Wolfgang Mueller, University of Paderborn, DE Tom Fitzpatrick, Mentor Graphics, US

The following 17 Special Sessions have been organised, which should prove to be of great general interest.

c special sessions

**Panel Sessions** provide a forum in which motivated opinions on a controversial issue are discussed. The 'trend setters' are given a timeslot to present their views, which are then subjected to critical appraisal from the audience. **Hot Topic** sessions give technical information about emerging new topics and provide a good overview and technical insight. Presenters are leading experts in the field. They present their view on the relevant issues and their importance for research and development. **Embedded Tutorials** give an insight of relevant topics usually starting from an introductory base.

- 2.4 Panel and Embedded Tutorial Logic Synthesis and Place and Route: After 20 Years of Engagement, Wedding in View? Organiser: M Casale-Rossi, Synopsys, US

- 2.8 Embedded Tutorial Addressing Critical Power Management Verification Issues in Low Power Designs Organiser: B Kapoor, Mimasic, US

- 3.8 Panel Session Power Formats: Beyond UPF and CPF Organiser: B Pangrle, Mentor Graphics, US

- 5.7 Embedded Tutorial Architectures for Online Error Detection and Recovery in Multicore Processors

- Organiser: D Gizopoulos, Piraeus U, GR 6.7 Hot Topic – Virtual Manycore Platforms: Moving Towards 100+ Processor Cores

- Organisers: R Leupers, RWTH Aachen U, DE and G Martin, Tensilica, US 6.8 Panel Session – Embedded Software Debug and Test

- Organiser: M Winterholer, Cadence, DE

- 7.7 Hot Topic Foundations of Component-Based Design for Embedded Systems Organisers: A Sangiovanni-Vincentelli, UC Berkeley, US and Trento U, IT and J Sifakis, VERIMAG, FR

- 7.8 Embedded Tutorial Predictable System Integration Organiser: W Kruijtzer, Synopsys, NL

- 8.7 Hot Topic Flows, Application and Future of Component-based Design for Embedded Systems Organisers: A Sangiovanni-Vincentelli, UC Berkeley, US and Trento U, IT and J Sifakis, VERIMAG, FR

- 8.8 Embedded Tutorial Communication Networks in Next Generation Automobiles

- Organisers: T Kazmierski, Southampton U, UK and C Grimm, TU Vienna, AT

Embedded Tutorial Sub-Wave Length Lithography and Variability Aware

- Test and Characterisation Methods Organiser: S Kundu, U of Massachusetts Amherst, US

- 10.7 Embedded Tutorial Die Stacking Goes Mobile and Embedded Organiser: A Jerrava, CEA-LETI MINATEC, FR

- 10.8 Panel Session –State of the Art Verification Methodologies in 2015 Organiser: T Fitzpatrick, Mentor Graphics, US

- 11.7 Hot Topic New Frontiers in Embedded Systems Design: Technology and Applications Organiser: G De Micheli, EPF Lausanne, CH

- 11.8 Hot Topic Stochastic Circuit Reliability Analysis in Nanometer CMOS Organiser: G Gielen, KU Leuven, BE

- 12.7 Hot Topic Sustainability through Massively Integrated Computing: Are We Ready to Break the Energy Efficiency Wall for Single-Chip Platforms? Organiser: R Marculescu, Carnegie Mellon U, US

\*

12.8 Hot Topic – Synthesis Supported Increase of Efficiency in Analogue Design Organiser: J Nowak, IMMS GmbH, DE

# event overview

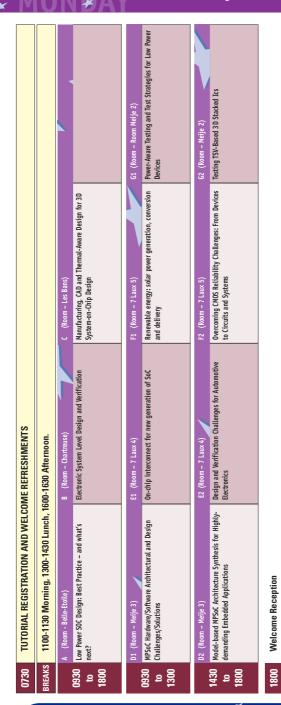

# MONDAY

Educational Tutorials Welcome Reception

# TUESDAY

Technical Conference and Exhibition Day 1 Vendor Exhibition Tool Seminars Exhibition Theatre (also featuring Track 8 special conference sessions) Opening Plenary, Keynote Addresses and Distinguished Awards Executive Sessions Lunch and Learn Session sponsored by Mentor Graphics Evening Reception offered by the City of Grenoble

# WEDNESDAY

Technical Conference and Exhibition Day 2 Vendor Exhibition Tool Seminars Exhibition Theatre (also featuring Track 8 special conference sessions) Smart Devices of the Future Special Day and Keynote DATE Awards Ceremony DATE Party

# THURSDAY

Technical Conference and Exhibition Day 3 Vendor Exhibition Tool Seminars Exhibition Theatre (also featuring Track 8 special conference sessions) Intelligent Energy Management – Supply and Utilisation Special Day and Keynote

# FRIDAY

Special Interest Workshops

# CONTACTS

7

#### DATE Event Secretariat European Conferences 3 Coates Place EDINBURGH EH3 7AA United Kingdom Tel: +44 131 225 2892 Fax: +44 131 225 2925

Conference and Speaker Enquiries Email: sue.menzies@ec.u-net.com

Exhibitor and Exhibition Enquiries Email: claire.cartwright@ec.u-net.com

#### monday 14 march

×

\*

www.date-conference.com

12

# tuesday 15 march

| BREAKFAST BREAKS 1030-1130 Exhibition Break, 1300-1430 Lunch, 1600-1700 Exhibition Break (1600-1630 IP1) | WARDS PRESENTATION, Auditorium Dauphine    |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------|

| BREAKS                                                                                                   | ES AND /                                   |

| ATION & SPEAKERS' BREAKFAST                                                                              | 0:80 1.1 PLENARY: OPENING, KEYNOTE ADDRESS |

| REGISTR                                                                                                  | 1.1 PLEN                                   |

| 0730                                                                                                     | 0830                                       |

×

|                    | SPECIAL TRACK                                                                                                  | PECIAL TRACK REFERENCE TECHNOLOGIES APPLICATIONS                                                                                                         | APPLICATIONS                                        | DESIGN TECHNOLOGY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TEST                                       | EMBEDDED SOFTWARE SYSTEM DESIGN      | SYSTEM DESIGN                                                                                                                                                    | SPECIAL SESSIONS                                                                                                    |

|--------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                    | Room – Oisans                                                                                                  | Room – Meije                                                                                                                                             | Room – Belle-Etoile                                 | Room – Belle-Etoile Room – Stendhal Room – Chartreuse Room – Bayard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Room – Chartreuse                          |                                      | Room – Les Bans 💦                                                                                                                                                | Exhibition Theatre                                                                                                  |

| 1130<br>to<br>1300 | 1130 2.1<br>to EXECUTIVE SESSION –<br>to EXECUTIVE SESSION –<br>teess on future of EDA<br>1300 and IP Industry | 2.2<br>System-Level Techniques<br>System-Level Techniques<br>to Handle Performance,<br>Reliability and Thermal<br>Issues                                 | 2.3<br>Modelling and Simulation<br>of Interconnects | 2     2.3     2.4 MNEL AND EMBEDDED     2.5     2.6       vistem-level Techniques     Modelling and Simulation     10/10/8/L/SSSDM - Logic     Transient Faults and Soft     2.6       vistem-level Techniques     Modelling and Simulation     Synthesis and Pace and<br>Synthesis and Pace and<br>Entors     2.6     Networked Embedded       Relation Expression     Synthesis and Pace and<br>Synthesis and Pace and<br>Entors     Entors     Systems       Relation Expression     Systems     Route: After 20 Verse of<br>Entors     Systems | 2.5<br>Transient Faults and Soft<br>Errors | 2.6<br>Networked Embedded<br>Systems | 2.7 2.8 EMBEDDED TUT<br>Design of Energy-Efficient - Addressing Critical<br>and Automotive Systems - Power Management<br>Verification Issues in<br>Power Designs | 2.8 EMBEDDED TUTORIAL<br>t – Addressing Critical<br>Power Management<br>Verification Issues in Low<br>Power Designs |

| 1400               | 3.0 SPECIAL LUI                                                                                                | 1400 3.0 SPECIAL LUNCH-TIME SESSION 1300-1400 Grenoble EDA Ecosystem Session - From Research to Market sponsored by Mentor Graphics, Auditorium Dauphine | 1400 Grenoble EDA Ecosys                            | stem Session - From Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | arch to Market sponsored                   | bv Mentor Graphics, Audi             | torium Dauphine                                                                                                                                                  |                                                                                                                     |

|                    |                                                                                                 |                                                                                                                                          |                                                               |                                                                  | וורוו וה הומו אבו שהחושהו בח                                   | ישט איניוועס אינייא איניי                                                                    |                                                              |                                                              |

|--------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|

|                    | Room – Oisans                                                                                   | Room – Meije                                                                                                                             | Room – Belle-Etoile                                           | Room – Belle-Etoile Room – Stendhal – Room – Chartreuse          |                                                                | Room – Bayard                                                                                | Room – Les Bans 🛛 🖌                                          | Exhibition Theatre                                           |

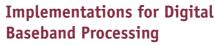

| 1430<br>to<br>1600 | 3.1<br>EXECUTIVE SESSION –<br>22nm Challenges and<br>Wealth/Knowledge<br>Creation Opportumities | 3.2<br>Power Optimisation of 3.3<br>Power Optimisation of Comen Agorithms for<br>Mutti-Core Architectures Forman Verification<br>Engines |                                                               | 3.4<br>Predicting Bugs and<br>Generating Tests for<br>Validation | 3.5<br>Timing Related Issues in<br>Test                        | 3.5<br>Timing Related Issues in Performance and Timing<br>Test                               | 3.7<br>Implementations for<br>Digital Baseband<br>Processing | 3.8 PANEL SESSION –<br>Power Formats: Beyond<br>UPF and CPF  |

|                    | Room – Oisans                                                                                   | Room – Meije                                                                                                                             | Room – Belle-Etoile                                           | Room – Stendhal                                                  | Room – Chartreuse                                              | Room – Bayard                                                                                | Room – Les Bans                                              | Exhibition Theatre                                           |

| 1700<br>to<br>1830 | 4.1<br>EXECUTIVE SESSION –<br>System Level Complexity<br>and Innovation                         | 4.2<br>Robust and Low Power<br>Systems                                                                                                   | 4, 3<br>Formal Verification<br>Techniques and<br>Applications | 4.4<br>System Level Simulation<br>and Validation                 | 4.5<br>Advances in Analogue,<br>Mixed Signal and RF<br>Testing | 4.6<br>Design Automation<br>Methodologies and<br>Architectures for Three-<br>Dimensional ICs | 4.7<br>Resource Management for R<br>QoS Guaranteed NoCs      | SEE WEB OR EVENT GUIDE<br>For latest exhibition<br>programme |

| 1830               | Evening Reception                                                                               | 1830 Evening Reception Offered by the City of Grenoble                                                                                   | f Grenoble                                                    |                                                                  | a                                                              |                                                                                              |                                                              |                                                              |

| 0230               | <b>REGISTRATION &amp;</b>                                                                   | REGISTRATION & SPEAKERS' BREAKFAST                                                   | BREAKS                                                                   | -1100 Exhibition Break                                            | 1000-1100 Exhibition Break, (1000-1030 IP2), 1230-1340 Lunch, 1600-1700 Exhibition Break (1600-1630 IP3) | 0-1340 Lunch, 1600-17                                                       | 00 Exhibition Break (                                                                                           | 1600-1630 IP3)                                                                            |

|--------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|                    | SPECIAL TRACK                                                                               | EMERGING TECHNOLOGIES APPLICATIONS                                                   |                                                                          | DESIGN TECHNOLOGY                                                 | TEST                                                                                                     | EMBEDDED SOFTWARE                                                           | SYSTEM DESIGN                                                                                                   | SPECIAL SESSIONS                                                                          |

|                    | Room – Oisans                                                                               | Room – Meije                                                                         | Room – Belle-Etoile                                                      | Room – Stendhal                                                   | Room – Chartreuse                                                                                        | Room – Bayard                                                               | Room – Les Bans                                                                                                 | Exhibition Theatre                                                                        |

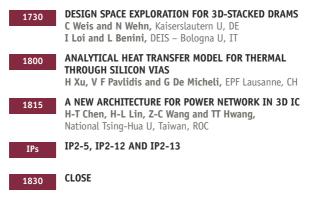

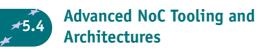

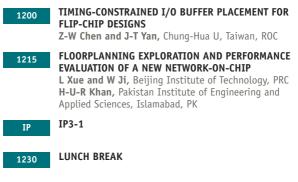

| 0830<br>to<br>1000 | 5.1<br>SMART DEVICES<br>EMBEDDED TUTORIAL –<br>Smart Devices for the<br>Cloud Era           | 5.2<br>An Encyclopedia of<br>Routing                                                 | 5.3<br>Temperature and Variation<br>Aware Design in Low<br>Power Systems | 5.4<br>Advanced NoC Tooling and<br>Architectures                  | 5.5<br>INDUSTRIAL 1                                                                                      | 5.6<br>Analysis, Compilation and<br>Runtime Techniques                      | 5.7<br>EMBEDDED TUTORIAL –<br>EMDEDDED TUTORIAL –<br>Error Detection and<br>Recovery in Multicore<br>Processors | EXHIBITION<br>OPENS AT 1000                                                               |

|                    | Room – Oisans                                                                               | Room – Meije                                                                         | Room – Belle-Etoile                                                      | Room – Stendhal                                                   | Room – Chartreuse                                                                                        | Room – Bayard                                                               | Room – Les Bans                                                                                                 | Exhibition Theatre                                                                        |

| 1100<br>to<br>1230 | 6.1.1<br>SMART DEVICES HOT<br>TOPIC/EMBEDDED<br>TUTORTAL – Ultra Low<br>Power Smart Devices | 6.2<br>Placement and<br>Floorplanning                                                | 6.3<br>Power Modelling, Analysis<br>and Optimisation                     | 6.4<br>Design and Test of Fault<br>Resilient NoC<br>Architectures | 6.5<br>New Techniques for<br>Diagnosis and Debug                                                         | 6.6<br>Embedded Software for<br>Parallel Architectures                      | 6.7<br>HOT TOPIC – Virtual<br>Manycore Platforms:<br>Moving Towards 100+<br>Processor Cores                     | 6.8<br>PANEL SESSION –<br>Embedded Software Debug<br>and Test                             |

| 1340               | 6.1.2 SPECIAL DA                                                                            | SPECIAL DAY KEYNOTE AND AWARDS 1340-1400 Awards and 1400-1430 Keynote, Room – Oisans | 1340-1400 Awards and                                                     | 1400-1430 Keynote, Roo                                            | ım – Oisans                                                                                              |                                                                             |                                                                                                                 |                                                                                           |

|                    | Room – Oisans                                                                               | Room – Meije                                                                         | Room – Belle-Etoile                                                      | Room – Stendhal                                                   | Room – Chartreuse                                                                                        | Room – Bayard                                                               | Room – Les Bans                                                                                                 | Exhibition Theatre                                                                        |

| 1430<br>1600       | 7.1<br>SMART DEVICES HOT TOPIC<br>- Smart Medical Implants                                  | 7.2<br>Emerging Memory<br>Technologies                                               | 7.3<br>Architectural<br>Optimisation for Low<br>Power Systems            | 7.4<br>Advanced Technologies for<br>NoC Implementation            | 7.5<br>Emerging Test Solutions<br>for Advanced<br>Technologies, RF and<br>MEMS Devices                   | 7.6<br>Innovative Power-Aware<br>Systems for a Green and<br>Healthy Society | 7.7<br>HOT TOPIC – Foundations<br>of Component-Based<br>Design for Embedded<br>Systems                          | 7.8<br>EMBEDDED TUTORIAL –<br>Predictable System<br>Integration                           |

|                    | Room – Oisans                                                                               | Room – Meije                                                                         | Room – Belle-Etoile                                                      | Room – Stendhal                                                   | Room – Chartreuse                                                                                        | Room – Bayard                                                               | Room – Les Bans                                                                                                 | Exhibition Theatre                                                                        |

| 1/00<br>1830       | 8.1<br>SMART DEVICES PANEL<br>SESSION - Interfaces<br>Real World Interfaces                 | 8.2<br>System-Level Design<br>Techniques for<br>Automotive Systems                   | 8.3<br>Power/Error Tradeoffs                                             | 8.4<br>Memory System<br>Architectures                             | 8.5<br>Testing and Designing<br>SRAM Memories                                                            | 8.6<br>Cryptanalysis, Attacks and<br>Countermeasures                        | 8.7<br>HOT TOPIC – Flows,<br>Application and Future of<br>Component-based Design<br>for Embedded Systems        | 8.8<br>EMBEDDED TUTORIAL –<br>Communication Networks<br>in Next Generation<br>Automobiles |

# FD FC wednesday 16 march

www.date-conference.com

\*

\*

# thursday 17 march

\*

| 0720               |                                                                                                                  | BEGISTRATION & SPEAKERS' BREAKEAST                                              | BPEAKS                                                                            | 1100 Evhibition Broal                                               | (1000-1030 IP4) 123                                            | 1.1330 Lunch 1530.16                                                     | 1000-1100 Exhibition Break (1000-1030 194) 1230-1330   unch 1530-1600 Break (1530-1600 195)                                    | 05)                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| nein               |                                                                                                                  |                                                                                 | DIEANS                                                                            |                                                                     | V 11000-1000 14                                                |                                                                          |                                                                                                                                | 1                                                                                          |

|                    | SPECIAL TRACK                                                                                                    | EMERGING TECHNOLOGI                                                             | A PLICATIONS                                                                      | DESIGN TECHNOLOGY                                                   | TEST                                                           | EMBEDDED SOFTWARE                                                        | SYSTEM DESIGN                                                                                                                  | SPECIAL SESSIONS                                                                           |

|                    | Room – Oisans                                                                                                    | Room – Meije                                                                    | Room – Belle-Etoile                                                               | Room – Stendhal                                                     | Room – Chartreuse                                              | Room – Bayard                                                            | Room – Les Bans 🖊                                                                                                              | Exhibition Theatre                                                                         |

| 0830<br>1000       | 9.1 INTELLIGENT ENERGY<br>MANAGEMENT TUTORIAL –<br>Energy Transfer,<br>Generation and Power<br>Electronics       | 9.2<br>Design Automation<br>Methodologies for<br>Emerging Technologies          | 9.3<br>System Modelling                                                           | 9.4<br>Modelling and Verification<br>of Analogue and RF<br>Circuits | 9.5<br>INDUSTRIAL 2                                            | 9.6<br>Embedded System<br>Resource Allocation and<br>Management          | 9.7<br>EMBEDDED TUTORIAL –<br>EMBEDDED TUTORIAL –<br>Lithography and<br>Variability Aware Test and<br>Characterisation Methods | EXHIBITION<br>OPENS AT 1000                                                                |

|                    | Room – Oisans                                                                                                    | Room – Meije                                                                    | Room – Belle-Etoile                                                               | Room – Stendhal                                                     | Room – Chartreuse                                              | Room – Bayard                                                            | Room – Les Bans 🖊                                                                                                              | Exhibition Theatre                                                                         |

| 1100<br>to<br>1230 | 10.1.1 INTELLIGENT<br>ENERGY MANAGEMENT –<br>Smart Energy Generation:<br>Design Automation and<br>the Smart-Grid | 10.2<br>Advanced Algorithms and<br>Applications for<br>Reconfigurable Computing | 10.3<br>System Optimisations and<br>Adaptivity                                    | 10.4<br>Design and Simulation of<br>Mixed-Signal Systems            | 10.5<br>Advances in Test<br>Generation and Fault<br>Simulation | 10.6<br>Model Based Verification<br>and Synthesis of<br>Embedded Systems | 10.7<br>EMBEDDED TUTORIAL –<br>Die Stacking Goes Mobile<br>and Embedded                                                        | 10.8<br>PANEL SESSION -State of<br>the Art Verification<br>Methodologies in 2015           |

| 1330               | 10.1.2                                                                                                           | L DAY KEYNOTE, 1330-140                                                         | SPECIAL DAY KEYNOTE, 1330-1400 Keynote, Room – Oisans                             | S                                                                   |                                                                |                                                                          |                                                                                                                                |                                                                                            |

|                    | Room – Oisans                                                                                                    | Room – Meije                                                                    | Room – Belle-Etoile                                                               | Room – Stendnal                                                     | Room – Chartreuse                                              | Room – Bayard                                                            | Room – Les Bans                                                                                                                | Exhibition Theatre                                                                         |

| 1400<br>1530       | 11.1 INTELLIGENT<br>ENERGY MANAGEMENT –<br>Smart Energy Utilisation:<br>From Circuits to Consumer<br>Products    | 11.2<br>Architectural Innovations<br>for Reconfigurable<br>Computing            | 11.3<br>Asynchronous Circuits and<br>Advanced Timing Issues in<br>Logic Synthesis | 11.4<br>High Level Synthesis                                        | 11.5<br>New Directions in Testing                              | 11.6<br>Hardware Design for<br>Multtimedia Applications                  | 11.7<br>HOT TOPIC – New Frontiers<br>in Embedded Systems<br>Design: Technology and<br>Applications                             | 11.8<br>HOT TOPIC – Stochastic<br>Circuit Reliability<br>Analysis in Nanometer<br>CMOS     |

|                    | Room – Oisans                                                                                                    | Room – Meije                                                                    | Room – Belle-Etoile                                                               | Room – Stendhal                                                     | Room – Chartreuse                                              | Room – Bayard                                                            | Room – Les Bans 🖊                                                                                                              | Exhibition Theatre                                                                         |

| 1730<br>1730       | 12.1<br>INTELLIGENT ENERGY<br>MANAGEMENT PANEL<br>SESSION – The Role of the<br>EDA Community                     | 12.2<br>Design and Run-Time<br>Support for Dynamic<br>Reconfigurability         | 12.3<br>Reliability and Error<br>Tolerance in Logic<br>Synthesis                  | 12.4<br>Reliability and Error<br>Tolerance in Logic<br>Synthesis    | 12.5<br>Error Correction and<br>Resilience                     | 12.6<br>Security Modules from<br>Layout to Network-on-<br>Chip           | 12.7<br>HOT TOPIC –<br>Sustainability through<br>Massively Integrated<br>Computing                                             | 12.8<br>HOT TOPIC – Synthesis<br>Supported Increase of<br>Efficiency in Analogue<br>Design |

|                    |                                                                                                                  |                                                                                 |                                                                                   |                                                                     |                                                                | 14-18                                                                    | 14-18 March 2011   Grenoble, France   DATE11                                                                                   | e, France DATE11                                                                           |

×

×

| 0230         | 0730 WORKSHOP REGISTRATION & WELCOME REFRESHMENTS                                            | STRATION & WELCON                                                                        | <b>AE REFRESHMENTS</b>                                                                                                                                                                                                                                                  |                                                                                             |                                                                                                                                                                                                                                                                  |                                                                                                 |                                                               |                                                |

|--------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------|

| BREAKS       | BREAKS Please see individual workshop programmes for lunch and break times                   | lual workshop progra                                                                     | mmes for lunch and b                                                                                                                                                                                                                                                    | reak times                                                                                  |                                                                                                                                                                                                                                                                  |                                                                                                 |                                                               |                                                |

|              | Room – Les Bans                                                                              | Room – Meije                                                                             | Room – Bayard                                                                                                                                                                                                                                                           | Room – Berlioz                                                                              | Room – Stendhal                                                                                                                                                                                                                                                  | Room – 7 Laux 4                                                                                 | Room – Belle-Etoile Room – Chartreuse                         | Room – Chartreuse                              |

| 0830<br>1700 | 0830 W1 Workshop on Micro<br>TO Prover Management for<br>Prover Systems on Chip<br>(uPM2S6C) | W2 Design Methods and<br>Tools for FPGA-Based<br>Acceleration of Scientific<br>Computing | W2 Design Methods and W3 Thrid Friday Workshop W4 Bringing Theory to Tools FPGA-Based on Designing for Embedded Practice Fredictability Acceleration of Scientific Amplitung Patforms and Performance in Architectures, Design Tools, Embedded Systems and Applications | W4 Bringing Theory to<br>Practice: Predictability<br>and Performance in<br>Embedded Systems | W5 3D Integration - W6 M-BED 2011, the 2nd W7 Hardware Dependent W8 1st International Applications. Technology. Workshop on Model Based Software Solutions for Soc QEMU Users Forum (QUF) Antineture. Dosign. Systems Design Automation, and feet Systems Design | W6 M-BED'2011, the 2nd<br>Workshop on Model Based<br>Engineering for Embedded<br>Systems Design | W7 Hardware Dependent<br>Software Solutions for SoC<br>Design | W8 1st International<br>QEMU Users Forum (QUF) |

\*

# friday 18 march

\*

\*

# TUTORIALS

#### Organiser: Luca Fanuci, Pisa U, IT

Eleven pre-conference tutorials will be given on Monday. Three are full-day tutorials (A, B and C). Eight are half-day tutorials, four to be given in the morning (D1, E, F1 and G1) and four in the afternoon (D2, E2, F2 and G2). A participant should enrol for either one full-day tutorial or one morning and/or one afternoon half-day tutorial (it is possible to attend for a morning or afternoon only in the case of the half-day tutorials). Combination of a full-day tutorial with a half-day tutorial is not allowed. Additional tutorial information can be found on the web – www.date-conference.com.

The titles, organisers, speakers, and abstracts of the tutorials are given below:

#### 0930

A

#### FULL-DAY TUTORIALS - A, B, C

(Room - Belle-Etoile)

Low Power SoC Design: Best Practice – and what's next?

Organiser: David Flynn, ARM, UK Speakers: David Flynn, ARM, UK Alan Gibbons, Synopsys, UK David Jacquet, ST-Ericsson, FR José Pineda de Gyvez, NXP, NL Praveen Raghavan, IMEC, BE

Low power design is an ever growing challenge and concern for designers, especially in battery powered consumer devices where both active and standby energy consumption and usable lifetime impact strongly on product success.

Active power management approaches such as Dynamic Voltage and Frequency Scaling, DVFS, are well understood but tough to put into practice industrially. Static power mitigation techniques such as Power Gating are increasingly required on advanced technology nodes with significant sub-threshold and gate leakage currents.

Over the last four or so years Electronic Design Automation tools have standardised on significant support for "multi-voltage" design and implementation and "power-intent" extensions to annotate RTL designs for supply voltage, power switching, isolating or clamping interfaces and inferring state retention.

In order to exploit these low power techniques effectively a systemlevel or architectural perspective increasingly matters in order to control and optimise the hardware layers of power management.

Understanding basic industrial best practice now, and how more advanced techniques can build on the existing multi-voltage tools support is a goal of this DATE 2011 tutorial that brings together presenters with a wealth of experience and expertise in real-world low power system design.

The invited presentations will cover theory and practice, starting with building blocks and components at the IP level and outlying methodologies for design, implementation and verification with the evolving power intent format standards (CPF and UPF).

Worked examples from multi-media and wireless application space will be addressed with a strong focus on practical design that works in production, and the areas of software and hardware partitioning and optimisation.

The tutorial will round off with a look at what is next on the low power roadmap for energy optimal design and research approaches to technology scaling and resilient and error tolerant design.

B

(Room - Chartreuse)

Electronic System Level Design and Verification

Organisers:

Thomas Bollaert, Mentor Graphics, US Carole Dunn, Mentor Graphics, US

Speakers:

Thomas Bollaert, Mentor Graphics, US Yvan Desmartin, STMicroelectronics, FR Michael Fingeroff, Mentor Graphics, US Bernhard Niemann, Fraunhofer Institute for Integrated Circuits, DE

Today's advanced designs have grown too massive and complex to cost-effectively design and verify using traditional RTL methods alone. Electronic System Level (ESL) design methods give designers the answers they need to overcome this dilemma. And of all the ESL methodologies flooding the market, the one technology that has gained considerable traction and use is high-level synthesis (HLS).

This tutorial explores the practical application of HLS with presentations from knowledgeable HLS users. In addition, Michael Fingeroff, the author of the High-Level Synthesis Blue Book, shares his guidance for how novices can go to experts by simply following the best practice coding examples shown in the book. Join us for a full-day of exploring how the promise of HLS is becoming a reality.

| C | (Room - Les<br>Manufacturi<br>System-on-C | ng, CAD and Thermal-Aware Design for 3D                                                                                                          |

|---|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Organisers:                               | David Atienza, EPF Lausanne, CH<br>Yuan Xie, Penn State U, US                                                                                    |

|   | Speakers:                                 | David Atienza, EPFL, CH<br>Tanay Karnik, Intel, US<br>Jeonghee Shin, IBM, US<br>Sachin S Sapatnekar, U of Minessota, US<br>P Leduc, CEA-LETI, FR |

Yuan Xie, Penn State U, US Three-dimensional integration (3D) with stacked chips is emerging as

an attractive solution for overcoming even further the barriers to interconnect scaling, thereby offering an opportunity to continue performance improvements using CMOS technology, with smaller form factor, higher integration density, and the support for the realisation of mixed-technology chips in multi-processor system-on-chip (MPSoC) designs. Consequently, 3D Integration technologies have become the focus of the recent semiconductor and IC design R&D activities worldwide, and recent advances in process technology have brought 3D technology to the point where it is feasible and practical, and it has raised widespread interest in the semiconductor and fab-less industry. However, adding the third dimension implies the redesign of EDA tools and design/architectural techniques to fully explore new approaches and address the additional challenges of the 3D manufacturing complexity. Moreover, 3D stacking creates even higher power and heat density, leading to degraded performance if thermal management is not handled properly in novel system-level design flows, which can combine mature multi-tier IC stacking manufacturing, appropriate 3D computer-aided design (CAD) tools and sensible hardware/software thermal-aware architectures for 3D MPSoCs.

×

×

The goal of this full-day tutorial is to provide a thorough overview of the complete design flow for 3D MPSoCs and mixed-design ICs, namely, starting from the 3D integration process technology up to the application and market drivers for 3D products, while covering the different system-level EDA related challenges in 3D MPSoCs, architectures for 3D MPSoC design and, finally, thermal modeling and management of MPSoC at the system level. Thus, this tutorial brings together leading 3D IC and MPSoC design experts in both industry/research centers (Intel, IBM, CEA-LETI) and academia (PennState, Univ. Minesota and EPFL), from both US and Europe, in order to cover in a comprehensive and structured way the key aspects of 3D technologies, design and products.

#### 0930

×

#### HALF-DAY TUTORIALS – D1, E1, F1, G1

#### D1 (Room - Meije 3) MPSoC Hardware/Software Architectural and Design Challenges/Solutions Organiser: Bernard Candaele, Thales, FR Speakers: Geert Vanmeerbeeck, IMEC, BE Kari Tiensyrjä and Jari Kreku, VTT, FI Axel Jantsch, KTH, SE Dimitrios Soudris, ICCS, GR Bernard Candaele and Sylvain Aquirre, Thales, FR

Multi-core SoCs are rapidly becoming main stream but raise numerous architectural hardware and software challenges in designing and programming. The tutorial will review state of the art, research and developments and next challenges for HW/SW architectures and design space exploration to implement multi-cores/many cores SoC or FPGA platforms for wireless and multimedia applications.

Mapping software onto multi-processor platforms requires efficient parallel programming techniques whilst achieving non-functional requirements. The fundamentals, design steps and alternative programming models to implement such embedded applications onto multi-cores are discussed and presented.

The need to accommodate a large number of applications on these massively parallel computing platforms requires the system engineer to quickly evaluate the performances of application mappings. The tutorial will review mainstream evaluation techniques based on simulation, abstract workload and processing capacity models.

On-chip and in-package memory organisation and efficient data management are key to high performance. The tutorial will review various memory architectures and techniques to address space management, cache coherency, memory consistency, and dynamic application specific memory allocation techniques.

The tutorial will conclude with a case study in telecom, reviewing current related studies and next challenges.

In summary, the tutorial will focus on the following topics:

- High level design space exploration of heterogeneous and customisable multi-core architecture based on abstract architecture and workload models representing the applications;

- Options and implications of the on-chip memory architecture covering central, distributed, private, and shared organisations;

- On-chip memory architectures and application specific dynamic memory allocation techniques for the considered multi-core architectures.

| E1 | (Room - 7 L  | (Room - 7 Laux 4)                                                                                                                                                          |  |

|----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|    | On-chip Inte | erconnect for New Generation of SoC                                                                                                                                        |  |

|    | Organisers:  | Marcello Coppola, STMicroelectronics, FR<br>Miltos Grammatikakis, TEI of Crete, GR                                                                                         |  |

|    | Speakers:    | Reinig Helmut, Infineon, DE<br>Luca Carloni, Columbia University, US<br>Raj Yavatkar, Intel, US<br>Michael Dimelow, ARM, UK<br>Philippe D'audigier, STMicroelectronics, FR |  |

On-chip interconnect design for embedded systems is moving away from traditional shared buses, such as AMBA AHB, IBM CoreConnect and STMicroelectronics STBus, towards sophisticated point-to-point communication architectures enriched by a set of services. The proliferation of multicore system-on-chip (SoC) and the desire to effectively consolidate applications in standardised platforms are driving forces of on-chip interconnect evolution. On-chip interconnects can benefit from knowledge transfer of PC. communication server and IT industry by embracing several wellknown technologies. However, due to critical challenges from complex applications and deep submicron technology, we must completely rethink our use cases and provide further enhancements for on-chip interconnects. New principles, constraints and processes are necessary for optimising system-level reuse, wire density, gate complexity, reliability, performance, scalability, power-efficiency and thermal management within the on-chip domain.

Within this context, this tutorial aims to evaluate the effectiveness of emerging innovative design methodologies, tools and leading-edge industrial practices for the evolution of on-chip interconnects in current state-of-the-art and next generation multicore SoC. Active researchers and well-established design managers firmly rooted in business realities and in tune with future trends will present important aspects and challenges within the vast and ever-changing world of on-chip interconnect technology, providing real life SoC examples.

A balanced, well-organised structure with strongly-connected presentations accompanied by numerous illustrations and easy-tounderstand examples will foster well-focused information exchange to the general embedded community, providing ample time for questions. The target audience includes mainly CS/EE professionals (e.g. hardware engineers, SoC architects and managers), as well as semiconductor vendors and investors.

(Room - 7 Laux 5)

Renewable Energy: Solar Power Generation, Conversion and Delivery

Organisers: Roberto Zafalon, STMicroelectronics, IT Francesco G Gennaro, STMicroelectronics, IT

Speakers: Francesco G Gennaro, STMicroelectronics, IT Gianluca Gigliucci, Enel, IT Salvatore Lombardo, IMM - CNR, IT Lars Bomholt, Synopsys, CH

Efficient generation, distribution and management of electric energy can reduce consumption in Europe from 20% to 30% by 2020 and CO2 emission in the same order of magnitude to achieve the Kyoto protocol targets and to limit the energy cost increase.

Solar energy generation proves to be a sustainable and efficient policy for global CO2 reduction. When coupled with the "Smart Energy Grid", it gives a reliable, flexible, accessible and yet cost-effective power source.

\*

×

F1

The Tutorial focuses on the solar energy supply chain, ranging from solar cells to innovative energy harvesting techniques, high efficiency power conversion and energy delivery through the smart grid.

The state-of-the-art and future trends of solar cells technology will be discussed, from standard Si cells to ultra-thin (20um) Si wafer PV cells, Si heterojunction cells, novel architectures (e.g. back-contact), new materials (for ARC, and passivation dielectrics), screen printing, laser processing and fully printable Dye-Sensitized-Solar Cells (DSSC). Next to the technology overview, the current status and features of system simulation of photovoltaic solutions using Synopsys TCAD Sentaurus for solar cell design and Saber for PV system simulation will be provided, suitable to model the thermally induced variations in performance.

Power conversion and control system design will be then addressed for a variety of cell technologies, with a special focus on Maximum Power Point Tracking operation.

Finally, energy delivery and transport will be the next challenge in the Smart Grid, with regards to management and control of electricity's exchange by means of communication infrastructure, either wired or wireless.

G1 (Room - Meije 2) Power-Aware Testing and Test Strategies for Low Power Devices Organisers: Yiorgos Makris, Yale U, US Dimitris Gizopoulos, Piraeus U, GR Speakers: Patrick Girard, LIRMM/CNRS, FR Nicola Nicolici, McMaster U, CA Xiaoqing Wen, Kyushu Institute of Technology, JP

Managing the power consumption of circuits and systems is now considered as one of the most important challenges for the semiconductor industry. Elaborate power management strategies, such as voltage scaling, clock gating or power gating techniques, are used today to control the power dissipation during functional operation. The usage of these strategies has various implications on manufacturing test, and power-aware test is therefore increasingly becoming a major consideration during design-for-test and test preparation for low power devices. This tutorial provides knowledge in this area. It is organised into three main parts. The first one gives necessary background and discusses issues arising from excessive power dissipation during test application. The second part provides comprehensive knowledge of structural and algorithmic solutions that can be used to alleviate such problems. The last part surveys low power design techniques and shows how these low power devices can be tested safely without affecting yield and reliability. EDA solutions for considering power during test and design-for-test are also discussed in the last part of the tutorial.

#### This tutorial is part of the annual IEEE Computer Society TTTC Test Technology Educational Program (TTEP) 2011

#### 1430

#### D2 (Room - Meije 3) Model-based MPSoC Architecture Synthesis for Highly-demanding Embedded Applications Organiser: Lech Jozwiak, TU Eindhoven, NL Speakers: Lech Jozwiak, TU Eindhoven, NL Menno Lindwer, SiliconHive, NL Jan Madsen, TU Denmark, DK

The recent spectacular progress in modern nanoelectronic technology enabled implementation of very complex multiprocessor systems on single chips (MPSoCs) and created a big stimulus towards development of high-performance systems for various highly-demanding embedded applications. In result, the increasingly complex and sophisticated MPSoCs are required to perform real-time computations to extremely tight schedules, with high demands regarding energy, power, area, and cost efficiency. Moreover, they are required to be flexible enough to enable reuse among different product versions, adherence to evolving standards or user requirements, and easy modification during their development or even their field use. This all results in serious design and development challenges, such as: multi-objective MPSoC optimisation, resolution of numerous complex design tradeoffs, reduction of the design productivity gap, time-to market and development costs without compromising quality, etc. The opportunities created can effectively be exploited only through use of more adequate application-specific system architectures and more integrated system IP modules, supported by new system-level design methods and EDA tools. This tutorial focuses on mastering the automatic architecture synthesis and application mapping for heterogeneous customisable multi-processor systems-on-chip (MPSoCs) based on configurable and extensible application-specific instruction-set processors (ASIPs). The MPSoC design technology based on adaptable ASIPs is able to deliver high performance, high flexibility and low energy consumption at the same time. It is relevant for a very broad range of modern applications and applicable to several implementation technologies. The tutorial presents the results of our analysis of the main problems that have to be solved and challenges to be faced in design of such heterogeneous customisable MPSoCs for modern demanding applications. It discusses the problems of architecture synthesis and application mapping involving multiobjective optimisation, adequate exploitation of multiple trade-offs, and coherent development of computing, communication and memory sub-systems for complex hard real-time embedded MPSoCs, as well as, proposes the model-based semi-automatic architecture synthesis methods and EDA-tools that enable effective and efficient solution of these problems.

E2 (Room - 7 Laux 4) Design and Verification Challenges for Automotive Electronics Organiser: Riccardo Groppo, Centro Ricerche FIAT, IT Speakers: Riccardo Groppo, Centro Ricerche FIAT, IT Patrick Leteinturier, Infineon, DE Erwan Hemon, Freescale, FR Pascal Caunegre, Freescale, FR Manfred Thanner, Freescale, FR Franco Toto, STMicroelectronics, IT Davide Appello, STMicroelectronics, IT Matteo Sonza Reorda, Politecnico di Torino, IT

\*

×

#### www.date-conference.com

The increasing complexity of automotive electronics, both in terms of electronic control systems' architecture and the new generation of complex ICs, must meet ever more demanding vehicle's requirements. On one hand the request for higher computational performances is due to more complex real-time mathematical models meant to achieve a better system control (i.e. improved combustion process for CO2 reduction); furthermore these mathematical models can also be designed to serve as "virtual sensors" in order to limit an overall system cost which is increasing day by day due to fuel economy and clean transportation increasing demands: this has been the driving factor of multi-core microcontrollers' architecture. The request for a better system partitioning and computational balance has also lead to the development of a new generation of mixed A/D intelligent ICs. On the other hand the need for improved reliability and, most of all, safety levels together with the stringent target cost, typical of the automotive business, is creating one of the biggest challenges at the silicon makers. In fact, automotive systems must have a high level of functional safety and fault tolerance built-in to ensure dependable and predictable operation over the lifetime of the product, which will be more than 10 years. The automotive-specific ISO 26262 safety standard defines the maximum acceptable failure rates and fault tolerant features that should be considered in the design and implemented in the development process. As a consequence modern design techniques and methodologies must be used in order to achieve those targets and predict system behavior in case of fault. Hence the tutorial will present basic and more advanced topics that cover various aspects of these challenges in a comprehensive fashion. It will start with the OEM view of the challenges, then advanced design methodologies, high level modeling, verification and statistical screening techniques will be described. The approach towards functional safety will require adequate efforts in terms of formal verification. Finally, an exhaustive testing automation and verification phase must be planned.

- F2 (Room 7 Laux 5) Overcoming CMOS Reliability Challenges: From Devices to Circuits and Systems

- Organiser: Yu (Kevin ) Cao, Arizona State U, US Subhasish Mitra, Stanford U, US Speakers: Yu (Kevin ) Cao, Arizona State U, US Georges Gielen, KU Leuven, BE Subhasish Mitra, Stanford U, US Sani Nassifi, IBM, US